# **Analog Circuit Optimization Based on Hybrid Particle Swarm Optimization**

Deepak Joshi<sup>†</sup>, Satyabrata Dash<sup>†</sup>, Ujjawal Agarwal<sup>‡‡</sup>, Ratnajit Bhattacharjee<sup>†</sup> and Gaurav Trivedi<sup>†§</sup>

<sup>†</sup>Department of Electronics and Electrical Engineering & <sup>§</sup>Center for Advanced Computing

Indian Institute of Technology Guwahati, Assam 781039, India

Email: {d.joshi(contact), satyabrata, ratnajit, trivedi}@iitg.ernet.in

<sup>‡‡</sup>Department of Electronics & Communication Engineering

PDPM Indian Institute Of Information Technology, Design and Manufacturing Jabalpur, Madhya Pradesh, India

Email: ujjawalagarwal@iitdmj.ac.in

Abstract—With growing Electronic Design Automation (EDA) industry, automated analog circuit design is now a feasible solution for the demand to exploit a span of nonlinear circuit behaviors from devices to circuits with the flexibility to optimize numerous competing continuous-valued performance specifications. In order to meet desired specifications, state-ofart EDA tools are employed which depend upon more efficient and effective optimization techniques to suffice the cost of designing complex analog systems. In this paper, a hybrid metaheuristic based on PSO and SA is presented to design one of the most prominent design specifications, i.e. gains of a two-stage CMOS operational amplifier circuit and a simple operational transconductance amplifier circuit subject to a variety of design conditions and constraints. Here convergence of PSO is improved by advancing through local solutions using SA to achieve quality global optimum solution. Experimental results are compared with other standard optimization techniques to show performance of proposed hybrid metaheuristic in terms of optimization quality and robustness.

Keywords-Electronic Design Automation; Particle Swarm Optimization (PSO); Simulated Annealing (SA)

#### I. Introduction

With the advent of electronic design automation (EDA) tools, the automation of analog circuit design is now a possible field of interest. As more analog design frameworks are being presented progressively in literature, it has become intrinsic to automate analog circuits for every elementary application. This can be achieved by introducing new design strategies to assure optimal solution in terms of design specifications, such as gain, power, slew rate etc. Then instead of relying on prior knowledge on systems, a particular circuit topology can be employed by one of the new design techniques to search for probable optimal solution of objective functions (specifications) subject to a variety of performance constraints.

In past, several proposals have been presented to automate the process of circuit designing [1], [2]. These proposals use a set of rules based on prior knowledge of circuits for automated designing according to a given set of specifications. They are proved to be fruitless, since it requires a lot of manual labor to create a new set of rules every time for new circuit topology. Later many techniques and tools are proposed to analyze the analog circuit design problem, such as ANACONDA [3], APE [4], optimization engines based

on evolutionary algorithms [5], [6], geometric programming [7], equation engines based on symbolic analysis [8] etc. In equation based symbolic analysis, circuit topology equations are used to translate the behavior of an analog circuit design problem into function optimization problem at the cost of accuracy and computational steps [5], [6]. Another proposal to analyze analog circuit design problem is the application of geometric programming method. Geometric programming method makes use of circuit topology to reach global optimum. However, this method demands additional computational steps in deriving a set of specific equations before having an input to the optimization engine [7]. On the contrary, heuristics based on evolutionary algorithms mimic behaviors of nature to provide optimum solutions to analog circuit design problem. Although many metaheuristics are available in literature [5], [6], [9], the simplicity and efficiency of particle swarm optimization (PSO) make it one of the favorable approaches to provide solution to a variety of problems like NP-complete problems [6], power systems [10], optimization problem [7] etc.

PSO is a population based parallel stochastic search method which mimics the behavior of swarms to look for global optimum through a multidimensional space [6]. Each swarm is considered as a particle in a multidimensional search space and the particles approach to optimum solution based on their history and basic characteristics, such as position and velocity of current particles and their neighbors. However, PSO has an inert disadvantage of being trapped locally and having slow convergence. In comparison, SA has a tendency to reach local optimum based on a serial stochastic search strategy [6]. Therefore to improve the search performance of PSO, a hybrid metaheuristic combining both PSO and SA is proposed in this paper to analyze the analog circuit designing problem. Several hybrid metaheuristics of PSO have already been presented in literature, such as PSO-GA [5], PSO-ACO [9], PSO-SA [6] etc. The hybrid PSO-SA metaheuristic proposed in [6] makes use of cooling strategy of temperature to avoid local traps and pursue a global optimum solution for multiprocessor task scheduling problem in a multi-stage flow shop environment. In this paper, using PSO different particles are allowed to move in the solution search space with random velocity values. Then

initial temperature is evaluated from velocity-temperature relation depending upon type of particles and accordingly multiple search spaces are chosen for different temperature ranges. Later the particles are allowed to move in those search spaces using SA to achieve optimum solution for analog circuit designing problem. Experimental results are compared with other standard optimization algorithms and it has been shown that search quality of proposed hybrid metaheuristic is better. To verify the effectiveness of the proposed hybrid metaheuristic, the solutions are compared with the solutions of Mentor Graphics Pyxis (Eldo).

The rest of the paper is organized as follows. A brief description of PSO and SA is given in section II. Section III deals with the proposed hybrid optimization approach. Section IV describes the effectiveness of proposed approach with a design example. Section V concludes the paper.

#### II. BRIEF DESCRIPTION

# A. Particle Swarm Optimization (PSO)

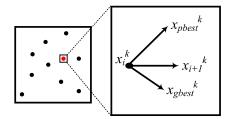

In particle swarm optimization, each particle is initialized with a random position in the multidimensional search space. Then the particle is allowed to move in the search space with random velocity. Fitness values are evaluated for each movement [11]. According to fitness values, personal best position of the particle (pbest) and global best position (gbest) among all particles are evaluated in each iteration. Using new personal and global best positions, the position (say x) and velocity (say v) of each particle are updated subject to a variety of design conditions [11] by using Equation 1 and Equation 2.

$$x_{i+1}^k = x_i^k + v_{i+1}^k \tag{1}$$

$$v_{i+1}^{k} = w_{i}v_{i}^{k} + C_{1}rand_{1}(x_{pbest}^{k} - x_{i}^{k}) + C_{2}rand_{2}(x_{gbest}^{k} - x_{i}^{k})$$

(2)

$$w_{i+1} = (w_{initial} - w_{final}) \left[ \frac{i_{max} - i}{i_{max}} \right] + w_{final}$$

(3)

where  $x_i^k$  and  $v_i^k$  denote position and velocity of particle k in  $i^{th}$  step respectively,  $C_1$  and  $C_2$  represent acceleration coefficients,  $rand_1$  and  $rand_2$  denote random numbers within range [0,1], w (< 1) represents inertia used for velocity calculation,  $w_{initial}$  and  $w_{final}$  denote the initial and final values of inertia w. For effectiveness of PSO, the values of acceleration coefficients  $C_1$  and  $C_2$  can be modified in each iteration by using Equation 4 [11].

$$C_1 = C_1^{initial} - \frac{2i}{n}, \ C_2 = C_2^{initial} + \frac{2i}{n}$$

(4)

where n, denotes number of iterations,  $C_1^{initial}$  and  $C_2^{initial}$  denote the initial values of  $C_1$  and  $C_2$  respectively and  $C_1^{initial} > C_2^{initial}$ . The trajectory of each particle towards personal and global best positions confirm the convergence to be globally optimum after satisfying specific design constraints. Figure 1 represents the movement of a particle in a two dimensional (2D) search space using PSO.

Figure 1: Performance of a particle in a 2D space using PSO.

#### B. Simulated Annealing (SA)

Simulated annealing is a stochastic heuristic that mimics the process, a metal is heated to a particular temperature and slowly allowed to cool down to its former state (annealing process) [6]. In analog circuit designing, SA is a well-known optimization technique, which is used to search for optimum solution by avoiding local traps. SA employs random searches to carry out the process of annealing not only in the gradient of minimization of objective cost function but may also allow to search in the direction of maximization indirectly. These indirect steps are allowed to happen during the process of annealing so that the occurrences of local traps can be prevented. It is required to develop a cost function (objective function) depicting the behavior of analog circuit, which defines the design specification to be optimized subject to a variety of design constraints before optimization using SA.

The random search of SA depends on the cooling effect of temperature. Let T(x) be temperature at any instant x. Before starting SA, the initial temperature is computed by taking the mean of various randomized solutions. With increase in time instant x, the change in temperature can be shown by using Equation 5 [6].

$$T(x+1) = \alpha T(x) \tag{5}$$

where  $\alpha$  is a constant which is generated in the range [0,1]. In each iteration, SA allows to search each step randomly based on a probability function f which leads to new states in solution space [6] and can be represented by using Equation 6 [6].

$$f = \frac{1}{Z_T} \exp \frac{-\Delta E}{T} \tag{6}$$

where  $-\Delta E$  is difference between new and previous solution,  $Z_T$  is normalization factor, T denotes the temperature ( $\downarrow$  0). Again if  $f > r_f$ , the new solution is accepted, where  $r_f$  has random values in the range [0,1]. The value of  $r_f$  is generated using probability density function [6].

$$r_f = \frac{1}{\sqrt{2\pi}\sigma} \exp\frac{-(x(i+1) - x(i))^2}{2\sigma^2}$$

(7)

where  $r_f$  denotes a random number function and value of  $\sigma$  denotes standard deviation. The tendency to reach an optimum solution depends upon the choice of cooling

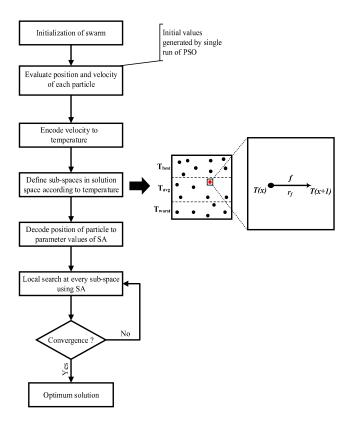

Figure 2: Block diagram representation of different steps in Hybrid PSO approach.

function T(t) and probability function f. During process of design using SA, if a step leads to a state having inefficient solution or no solution, the new state is allowed to have f < 1.

#### III. PROPOSED HYBRID OPTIMIZATION APPROACH

This section depicts the proposed optimization approach to design analog circuits for certain design parameters through a hybrid PSO metaheuristic, which integrates the advantages of both PSO (fast convergence rate) and SA (avoid local traps). In this hybrid approach, the process of annealing is utilized to pursue the search for optimum solution so that premature convergence of PSO can be avoided. PSO contributes to the hybrid approach in a way to ensure that the random search converges faster within the solution space, while SA takes care of local traps. Hybrid approach employs the exploration capability of both PSO and SA, and neutralizes the weaknesses of each. If SA is going to be performed at each iteration along PSO, the cost of computations will increase arbitrarily and at same time convergence rate of PSO may be weakened. In order to have quality of solution and to minimize the computational cost by integrating PSO with annealing process, SA is performed after completion of PSO. Therefore, the proposed hybrid PSO metaheuristic is able to sustain fast convergence rate of PSO algorithm even if it is enabled to perform with the aid of SA.

In hybrid PSO, each particle position  $x_i \ (\in N)$  is initialized with a uniform random number by using random() or given value of any design constraint to start with. Then fitness value is evaluated according to the particle having personal best  $(x_{pbest})$  and global best  $(x_{gbest})$  position. The fitness value is regarded as the objective function which serves as a solution for each displacement of particle in the solution space. After each iteration, the particle moves within the solution space with a random velocity. After a single complete run of PSO, velocity values of different particles are encoded to evaluate different temperatures using Equation 8. Then the multidimensional search space is divided into different swarm sub-spaces according to initial temperature values associated with each particle.

$$T = \beta(V_{rms}^2) \tag{8}$$

where  $\beta$  is a constant which depends upon the crystal property ( $\simeq$  metal conductivity mechanism) of particle and  $V_{rms}$  denotes the root mean square velocity of all particles of a sub-space and can be evaluated by using Equation 9.

$$V_{rms} = \sqrt{(V_{x_1})^2 + (V_{x_2})^2 + \dots + (V_{x_n})^2}$$

(9)

Later the particles are allowed to move in each sub-space using the process of annealing (SA) to perform local search for any traps and one global optimum solution is selected among the local optimum solutions by looking at the behavior of the fitness values evaluated in each sub-space.

#### IV. ANALOG CIRCUIT OPTIMIZATION PROBLEM

Analog circuit design is generally observed to be less reliable and more heuristic in nature than digital design due to variations in circuit device properties, different circuit schematics, design requirements and specifications. The presence of such variations leads to extreme conditions which makes analog circuit design process a daunting task for a circuit designer. Every analog circuit design process comes with certain operating conditions (temperature, supply voltages, bias currents etc.) and tradeoffs [12] among design specifications. The tradeoffs confine the circuit design to a solution space instead of a single solution. Circuit response bounded by these tradeoffs, can be formulated as an objective function for optimization process subject to a variety of circuit specifications. An example of such objective function can be seen in Equation 10.

$$\begin{array}{ll} \text{maximize} & h_0(x) \\ \text{subject to} & h_k(x) \leq 1 \;, \qquad k \in R \\ & p_i(x) = 1 \;, \qquad i \in R \\ & x_j > 0 \;, \qquad j > 2 \end{array} \tag{10}$$

where  $h_0(x)$  is the objective function and  $h_k(x)$ ,  $p_i(x)$  &  $x_j$  denote design constraints.

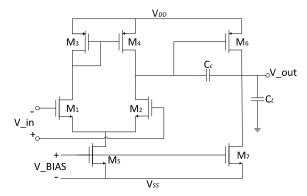

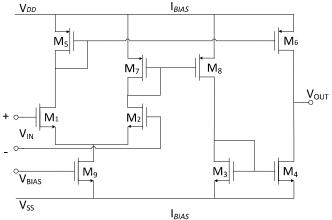

Figure 3: Two-stage operational amplifier circuit. [12]

Table I: Constraints and specification for two-stage operational amplifier. [12]

| Constraints                        | Specification  |

|------------------------------------|----------------|

| Open-loop gain ( $A_{dc}$ )        | Maximize       |

| Unity gain bandwidth ( $w_0$ )     | $\leq 5 MHz$   |

| Slew rate ( $SR$ )                 | $> 10 V/\mu s$ |

| Input common-mode range ( $ICMR$ ) | -1 to 2V       |

| Output voltage swing               | $\pm 2V$       |

| Load capacitance                   | 10 pF          |

| Phase Margin                       | $\geq 60 \deg$ |

# A. Design Example 1: Two-stage Operational Amplifier

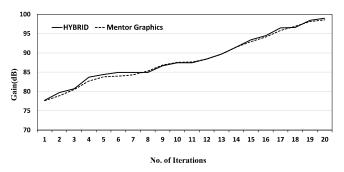

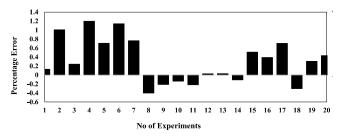

A two-stage operational amplifier circuit [12] as shown in Figure 3 is taken as a benchmark to show the effectiveness of proposed approach. The solutions obtained by using the proposed approach is verified with the solutions of Mentor Graphics layout tool Pyxis as shown in Figure 4 and an average of 0.3% relative error is found to be reported using the mathematical Equation 11. Figure 5 represents the percentage error calculated for twenty experiments.

% of

$$error = \frac{A_v^{hybridPSO} - A_v^{Mentor}}{A_v^{hybridPSO}} \times 100$$

(11)

For designing of two-stage operational amplifier, open-loop gain is taken as an objective function subject to the constraints as shown in Table I. The objective function, i.e. gain  $A_v$  can be formulated as a function of transconductances  $(g_{m1}, g_{m2}, \ldots, g_{m7})$  and channel resistances  $(r_{o1}, r_{o2}, \ldots, r_{o7})$  of transistors of the two-stage operational amplifier circuit. Then the absolute value of voltage gain  $A_v$  can be represented as [12],

$$|A_v| = \frac{g_{m2} \times g_{m6}}{(g_{ds2} + g_{ds4}) \times (g_{ds6} + g_{ds7})}$$

(12)

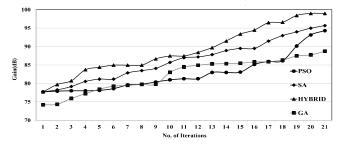

where,  $g_{dsi}=1/r_{oi}$ , for i=2,4,6 and 7. The transconductance vector Gm ( $g_{m1}$ ,  $g_{m2}$ , $g_{m5}$ ) is treated as position of particles for application of the proposed hybrid PSO approach. Experiments are performed on two-stage amplifier circuit to maximize gain parameter subject to the

design constraints listed in Table I using GA, PSO, SA and the proposed hybrid PSO approach and the solutions are shown in Figure 6. From Figure 6, it can be seen that the performance of proposed hybrid PSO metaheuristic is better in terms of providing quality solution than other techniques. The use of SA in hybrid PSO metaheuristic ensures prevention of falling into local traps. As SA is performed in different temperature regions  $(T_{best}, T_{avg}, T_{worst})$  simultaneously, the computational performance of hybrid PSO approach is not affected in a significant manner. For this design example, we have taken different temperature regions  $T_{best}, T_{avg}$  and  $T_{worst}$  by using the relations given in Equation 13. Here  $\delta T$  denotes  $T_{max} - T_{min}$ .

$$0 < T_{worst} < \frac{\delta T}{3}, \quad \frac{\delta T}{3} < T_{avg} < \frac{2\delta T}{3},$$

$$\frac{2\delta T}{3} < T_{best} < \delta T \qquad (13)$$

Figure 4: Design verification of proposed hybrid PSO approach with Mentor Graphics Pyxis tool for maximum gain of a two-stage operational amplifier circuit.

Figure 5: Percentage error for different experiments for the design of twostage operational amplifier circuit.

Figure 6: Comparison of different optimization techniques with proposed hybrid PSO approach for maximum gain of a two-stage operational amplifier circuit.

For sake of completeness, twenty number of experiments are carried out for the design of two-stage operational amplifier circuit using proposed hybrid PSO, PSO and SA. The solutions and the time required for computation are listed in Table II.

Table II: Optimal gain obtained after execution of different heuristics for 20 experiments for the design of two-stage operational amplifier circuit and corresponding execution time of different heuristics

| Performance Parameters | SA    | PSO   | $PSO_{hybrid}$ |

|------------------------|-------|-------|----------------|

| $A_v^{optmin}$ (dB)    | 83.9  | 85.33 | 88.67          |

| $A_v^{optavg}$ (dB)    | 89.87 | 88.84 | 92.99          |

| $A_v^{optmax}$ (dB)    | 96.67 | 94.30 | 99.00          |

| $t_{comp}$ (ms)        | 0.551 | 0.432 | 0.7095         |

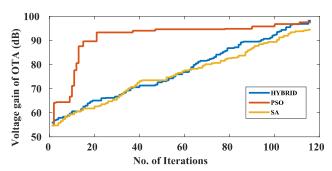

# B. Design Example 2 : Operational Transconductance Amplifier

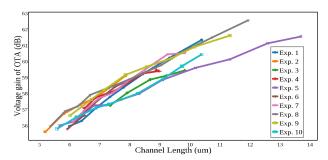

Operational transconductance amplifiers (OTAs) have been used as one of the representatives of general purpose circuits due to high transconductance and voltage gain in moderate inversion region. For showing the effectiveness of the proposed hybrid PSO approach, a simple OTA circuit as shown in Figure 7 is taken as a design example to be operated in weak or moderate inversion region at long channel lengths. Here voltage gain  $(A_v^{OTA})$  of the simple OTA circuit is maximized by using the proposed hybrid PSO approach by operating transistors at long channel lengths for high transconductance  $(g_m)$  and high drain-to-source resistance  $(r_{ds})$ . The voltage gain  $(A_v^{OTA})$  of the OTA circuit can be approximated by Equation 14 [13].

$$A_v^{OTA} = G_m^{OTA} \times R_{out}^{OTA} \tag{14}$$

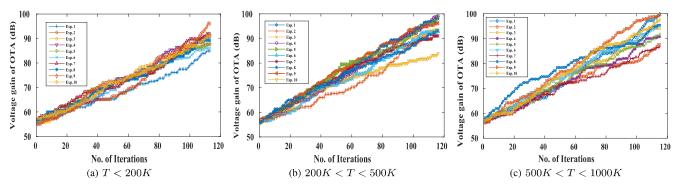

where  $G_m^{OTA}$  and  $R_{out}^{OTA}$  denote transconductance and output resistance of simple OTA circuit respectively. It can be devised from the operation of OTA in inversion regions (weak or moderate) that  $A_v^{OTA}$  decreases with the increase in inversion coefficient regardless of the magnitude variation in OTA bias current ( $I_{bias}^{OTA}$ ) and increases sublinearly with the increase in the transistor channel lengths  $(L_4 \& L_6)$  [13]. Various experiments are performed on OTA circuit to maximize the voltage gain subject to inversion coefficient and long channel lengths of transistors using standard optimization techniques such as PSO & SA, and the proposed hybrid PSO approach which is shown in Figure 8. Figure 8 shows that the convergence of PSO is faster as compared to the proposed hybrid PSO approach. However, the performance of proposed hybrid PSO metaheuristic is better in terms of achieving maximal gain values at best temperatures (500K < T < 1000K). The particles at high temperature region take maximum amount of time to cool down than the particles of other regions. Eventually this annealing process assists in search of finding out the local optimum. The proposed hybrid PSO approach guarantees in

Figure 7: A simple operational transconductance amplifier circuit. [13]

Figure 8: Comparison of different standard optimization techniques with hybrid PSO approach for maximum gain of a simple operational transconductance amplifier circuit.

finding a solution regardless of the objective function values and design constraints. Figure 9 represents the variation of gain parameter of simple OTA circuit with respect to change in long channel lengths  $(4\mu m - 14\mu m)$  of transistors  $(M_1 \ to \ M_4)$  for a maximum of ten experiments  $(taking\ inversion\ coefficient\ to\ be\ a\ constant\ in\ all\ experiments).$  Figure 10 represents optimization using proposed hybrid PSO approach for maximum gain of a simple OTA circuit in three different temperature regions and it can be seen that a maximum gain of around 100dB has been achieved by one of searches done by hybrid PSO metaheuristic in the region

Figure 9: Variation of voltage gain in dB with respect to variation in long channel length using hybrid PSO approach for a simple operational transconductance amplifier circuit.

Figure 10: Optimization using hybrid PSO approach for maximum gain of a simple OTA circuit in three different temperature regions.

having high temperatures (500K < T < 1000K). One of the reasons for this maximum gain may be the impact of high temperature on the cooling strategy of SA approach. At high temperature, particles tend to move with high velocity within the multidimensional search space and it will give enough computational space to the search strategy of SA approach to come out of local traps to settle for global optimum solution.

#### V. CONCLUSION

A method of circuit optimization using hybrid PSO metaheuristic to optimize an analog circuit is proposed and the effectiveness of the proposed method is shown by verifying the solutions of a two-stage cascode amplifier circuit with the solutions of Mentor Graphics Pyxis (Eldo) tool. It is found that the solution of the proposed hybrid metaheuristic falls in with the solutions provided by Mentor Graphics Pyxis tool with an average of 0.3% error. It is observed from comparison of the solutions of proposed hybrid metaheuristic with other standard optimization techniques that the proposed hybrid PSO approach is better in providing quality solutions without affecting the rate of convergence in a significant manner. In future, authors intend to generalize the selection process of global solution from local optimum solutions provided by SA in different temperature regions. In addition, the robustness of proposed hybrid PSO metaheuristic can be exploited by taking design examples of RF and microwave circuits.

#### ACKNOWLEDGMENT

The authors would like to acknowledge Center for Advanced Computing, IIT Guwahati for providing computing resources to conclude this research work.

# REFERENCES

[1] G. Gielen, H. Walscharts and W. Sansen, "Analog circuit design optimization based on symbolic simulation and simulated annealing," *IEEE Journal on Solid-State Circuit*, vol. 25, no. 3, pp. 707–713, Jun 1990.

- [2] R. Schwencker, J. Eckmueller, H. Graeb and K. Antreich, "Automating the sizing of analog CMOS circuits by consideration of structure constraints," in *Design Automation and Test in Europe*, Germany, pp. 323–327, 1999.

- [3] R. Phelps, M. Krasnicki, R. A. Rutenbar, L. R. Carley, and J. R. Hellums, "ANACONDA: Simulation-based synthesis of analog circuits via stochastic pattern search," *Trans. Comp.-Aided Des. Integ. Cir. Sys.*, vol. 19, no. 6, pp. 703–717, Nov. 2006.

- [4] G. Venkatesh, "APE: Accelerator processor extensions to optimize data-compute co-location," in *Proceedings of the ACM SIGPLAN Workshop on Memory Systems Performance and Correctness*, New York, pp. 1–10, 2013.

- [5] Y. Kao and E. Zahara, "A hybrid genetic algorithm and particle swarm optimization for multimodal functions," *Applied Soft Computing*, vol. 8, no. 2, pp. 849 857, 2008.

- [6] X. Song, Y. Cao, and C. Chang, "A hybrid algorithm of PSO and SA for solving JSP," in Fuzzy Systems and Knowledge Discovery, 2008. FSKD '08. Fifth International Conference on, vol. 1, pp. 111–115, Oct. 2008.

- [7] P. Mandal and V. Visvanathan, "CMOS OpAmp sizing using a geometric programming formulation," *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on*, vol. 20, no. 1, pp. 22–38, Jan 2001.

- [8] M. Shokouhifar and A. Jalali, "Automatic symbolic simplification of analog circuits in MATLAB using ant colony optimization," in *Electrical Engineering (ICEE)*, 2014 22nd Iranian Conference on, pp. 407–412, May 2014.

- [9] T. Niknam and B. Amiri, "An efficient hybrid approach based on PSO, ACO and k-means for cluster analysis," *Applied Soft Computing Journal*, vol. 10, no. 1, pp. 183–197, 2010.

- [10] V. Pappala and I. Erlich, "Power system optimization under uncertainties: A PSO approach," in Swarm Intelligence Symposium, 2008. SIS 2008. IEEE, pp. 1–8, Sep. 2008.

- [11] A. Ratnaweera, S. Halgamuge, and H. Watson, "Self-organizing hierarchical particle swarm optimizer with time-varying acceleration coefficients," *IEEE Transactions on Evolutionary Computation*, vol. 8, no. 3, pp. 240–255, Jun. 2004.

- [12] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design. USA, Sep 2011.

- [13] A. Gratz, "Operational Transconductance Amplifiers," 2006.