# **SESSION**

# MICRO-CONTROLLERS, MICRO-PROCESSORS, PROGRAMMING, SOFTWARE SYSTEMS AND RELATED ISSUES

# Chair(s)

### TBA

## Lumousoft Visual Programming Language and its IDE

#### Xianliang Lu

Lumousoft Inc. Waterloo Ontario Canada

**Abstract** - This paper presents a new high-level graphical programming language and its IDE (Integration Development Environment) for microprocessor-based embedded system. The graphical programming language allows programming in the graphical block diagram environment. In comparison with textual programming languages, it allows direct bit operation, and enables to program or lay out complicated networks for cognitive algorithm application. With the trace analyzer, the graphical language can fully recycle memory, reduce reductant code to reduce the cost, and improve performance. The graphical structure including basic units, layout format and modules are described in details. This new graphical language provides great convenience for embedded software maintenance, coding, verification, validation and reusable components.

Keywords: graphical; module; programming; language; IDE

#### **1** Introduction

With the increasing complexity and sophistication of electronics device, the more efforts are put on embedded software that plays a pivotal role in electronic industry. There are great demands for more efficient, productive and reliable software-developing tool to facilitate embedded software design, development and maintenance.

It is proved that the blueprint is the most efficient way in engineering practice for design, validation, verification, test, maintenance and modification. Embedded software is more restrict and complex than other software field due to real time and reliability. Embedded software faults might cause serious damage to electronic device. An embedded software engineer or developer usually has electronic background and familiar with blueprints. But current embedded software design and development have to be on the text-based platform that is hard to read and catch the whole map of software project. Consequently, developing software has to take more efforts and much more time than other engineering fields like electricity, mechanics.

C/C++ language is a dominant language in embedded system due to similarity to assembly language and more readability. Comparing with assembly language, C/C++ compiler might generate bigger size of machine codes and use up more memory, sometimes may cause memory leakage and memory conflict or boundary corruption, yielding more cost in hardware and poor quality of performance. Because it has more readability and efficiency than assembly language, it still gains dominant application in the embedded field.

In addition to textual language, visual programming language (VPL) begin to be found application in embedded system like flowcode produced by Matrix Multimedia for programming embedded devices. Most of VPL languages have limit application and less flexibility because programming capability depends on how many graphical components available from VPL provider.

Lumousoft graphical language is a visual programming language for microprocessor allowing programming in block environment with high usage of hardware resource and high quality of performance. This graphical language not only has the same programming capability as textual language such as C but also enables to program complex network for cognitive algorithm application.

#### 2 Syntactic structure

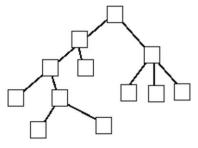

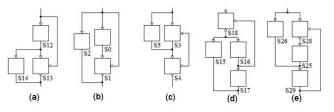

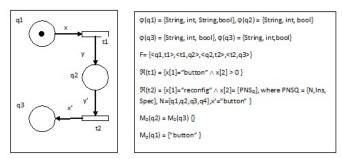

Lumousoft graphical language is a programming language in block environment. In general, the textual language uses textual statement to represent flowing program path in the form of parse tree, and each tree branch is not allowed to be interconnected , an example parse tree is shown in Fig.1. Unlike textual language, Lumousoft graphical language uses block, connection line and direction symbol to form program flowing pattern, the block diagram connection pattern is not limited to parse tree, allowing branches to be interacted to form complicated networks. An example is illustrated in Fig.2 . In lumousoft graphical language, a path analyzer is employed to analyze the program pattern including loop.

Fig. 1. Textual language parse tree

Lumousoft graphical language uses path analyzer to indentify block connection pattern other than parse tree, However, in each block are there multiple lines of expression for logic or arithmetic operation, these lines of instruction are

formats. With these basic layout units, a complicated network

arranged in executable sequence without jumping branch. While, each line of expression still follows parse tree for analysis and compilation.

Fig. 2. Block network

Lumousoft graphical language employs path analyzer to determine network. This mechanism is different from current textual language syntactic structure and allows lumousoft graphical language to handle more complicated network to accomplish the more complex and sophisticated task.

#### **3** Layout format

#### 3.1 Basic unit

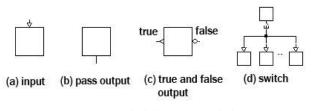

Lumousoft graphical language is made of four units: block, line, direction and statements in a block. The block contains executable statement, which performs logic and arithmetic operation; line is to build connection between blocks; direction determines how the process flows. The symbol of direction is shown in Fig. 3 there are two class directions, input and output. The output can be divided further into non-conditional output (pass output) and conditional outputs (pair of true and false output and switch).

Fig. 3. Block direction symbols

Because lumousoft graphical language is a programming language, the program codes need to be modified form times to times, the symbol or shape of graphic icon might change accordingly, this will cause great inconvenience for developer and waste a lot of time to adjust symbol or icon. Therefore, Lumousoft graphical language does not adopt the standard flowchart symbols, just employs block for ease of programming.

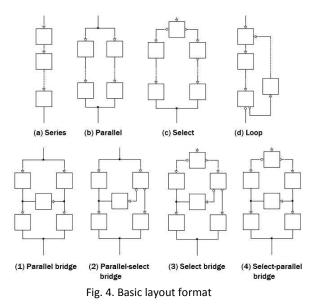

#### 3.2 Connection models

The block layout can be in the form of series, parallel, selection, loop and bridges. Fig. 4 illustrates the basic layout

#### 3.3 Series

can be created.

Similar to series circuit, the program executes in sequence.

#### 3.4 Parallelism

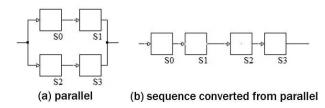

In our daily life, parallelism exists like electrical circuit. The current Lumousoft language version is applied to single chip microprocessor, not for multi-cores. In order for single core to handle parallelism, the parallel branches need to be rearranged and connected in sequence. Fig.5. demonstrates the conversion of parallel to sequence.

Fig. 5. Transformation form parallel to sequence

The parallelism that lumousoft graphic can handle should meet the following condition.

Fig. 6. Illegal parallel connection

- Parallel branches should have start terminal and end terminal. Just like electrical circuit, if the branches start from some point without join later, it will cause error.

- The branch after joined terminal will not be executed until all the join branches have been executed, in other words, if a branch after parallel join is executed before any parallel branch will cause error.

- Except the bridge connection (Contrained to 2 parallel branches) as shown in Fig.4 (2) and Fig.4 (4), the parallel branch is not allowed to be joined in or jump out of parallel by a decision path. Fig.6 shows some examples of illegal parallel patterns.

The parallel connection can be nested in a loop or contains a loop as shown in Fig. 7 (a) and (b). Parallel connection can be as complicated as Fig.7 (c) shows.

Fig. 7. Parallel connection samples

#### 3.5 Selection and Loop

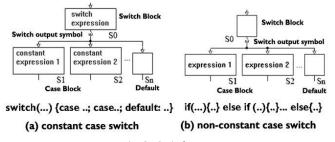

The selection branches either consist of true and false branches coming from decision block or switch clause blocks as shown in Fig.3. (c), (d) respectively.

In true false selection branch, which branch will be flowed from decision block depends on the last line of statement in the decision block. If the value of last statement in the decision block is non-zero value or true, the program will flow to true branch; if the value of last statement in the decision block is zero or false, the program will flow to false branch.

Switch consists of switch block and case blocks. The switch block is the block attaching a switch output symbol.

#### Fig. 8. Switch

While, the case block is the one which input is connected to the switch symbol as shown in Fig. 8. The switch can be categorized into constant case switch and non-constant case switch. As the name implies, when case blocks contain constant expression we call constant case switch, the switch

path goes to the case block where the switch expression at the last line of statements in switch block matches the value of constant expression in the case block. Fig.8 (a) illustrates constant case switch.

While, non-constant case switch is that when case blocks contain non-constant expression. Fig.8 (b) shows the nonconstant case switch. The non-constant case switch is more like the clause "if .. else if .. else.." of textual language. The process path is selected when the value of case block expression first turn out to be true or non-zero. The check-up for true takes place from the left to the right if all case blocks lay out horizontally, and from the top to the bottom if case blocks lay out vertically.

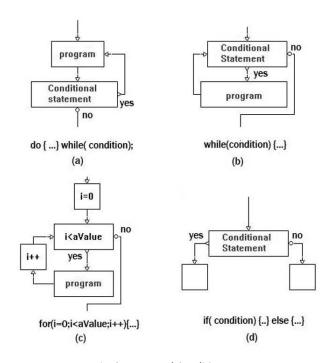

Fig. 9. Loop and Condition

In Lumousoft language, switch must contain only one default case block. The default case block is defined when the content of a case block is empty or blank.

By selection block, complicated network including loop can be created. In C language, it uses statement to represent loop and condition like "switch(..){case..; case..; ..; default: ..;}","if(){..}else if(..) {..}..else {..}", "do...while (condition);", "for()", " while(){..} ", "if().. else ". Fig.8. and Fig.9. illustrates graphical expressions for above textual expressions.

#### 3.6 bridges

Fig.4 (1)-(4) show four kinds of basic bridges. With these basic bridges, lumousoft language is able to design complex algorithm with less efforts.

#### 4 Variable

Like other programming languages, Lumousoft graphical language has local, global, system, constant, array pointer variable. Except the regular data type, lumousoft graphical language has bit variable that is especially helpful for microprocessor application. As soon as a variable is defined, the variable can be accessed in the whole scope where the variable stays. There is no need to make declaration of variable.

#### 4.1 Memory Optimization

Because lumousoft graphical language adopts block network instead of parse tree, tremendous memories might be required. The memory size is one of factors that affect the price of microprocessor. The bigger size of memory the more expensive microprocessor is.

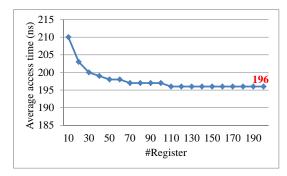

A variable usually is assigned a memory or register to store a special value. When the content of a memory is written and the previous value of the memory is lost, we can say that the previous value is dead and the variable associated with this dead value die too. While, when the memory is written a new value, the variable associated with this memory is born. A variable has life span from the variable is assigned a new value to the last time usage before the memory was override. The variable might alive and die for many times in a program.

Lumousoft graphical language takes the advantage of trace analyzer to indentify the life span of a variable, When a memory is born or created, a memory will be allocated to the variable, and when the variable is dead the associated memory will be released and ready for a new variable. Because global, static, system variables have permanent life, only the local memory is going to be optimized in lumousoft graphical language.

#### 4.2 Bit Variable and Operation

Bit is the atomic data type of data. Current high level languages like c does not allow directly operating on bit, usually using indirect way like byte bitwise operation. Lumousoft graphical language allows direct operate on bit. Here, the variable holding the bit variable is called as bit source variable, and where the bit sits in a bit source is called bit position value.

The bit variable can be defined in the variable manager dialog of IDE or use the below statement to define:

$$bitVar = \&(sourceVar \# positionVal)$$

(1)

Or uses the below expression to represent a bit variable

$$sourceVar \# positionVal \tag{2}$$

where

bitVar - bit variable

sourceVar- bit source variable

positionVal- bit position in the bit source variable

A bit value can be 0 or 1 like Boolean, when bit work with non-bit data type variable or in logical operation, the bit variable is treated as a Boolean variable. When the bit is set the Boolean value is 1, and the bit is reset, the Boolean value 0. Therefore, when a bit variable works with other non-bit variable it works as Boolean similar to other language like c.

When a bit variable works with other bit variable it will operate according to bit value. The bit operation can be:

and assign(&=), or assign(/=), xor  $assign(^=)$ .

When a bit source variable consists of more than one byte, lumousoft graphical compiler will use expressions (3) and (4) to find the byte that bit stay and find out the correct bit position.

$$nByte = floor(bitPos / sysBitLen)$$

(3)

$$nPos=bitPos \% sysBitLen$$

(4)

Where

*nByte* - the byte where the concerned bit stay.

*nPos* – the bit position in the *nByte*

*floor* - a function to get the round down integer value

*bitPos* – bit position

*sysBitLen* – The bit number of memory that microprocessor can handle

For example a bit variable is fifteenth bit of a bit source, the bit source is short data type and supposed that it is allocated by 2 bytes with the address of 0x20 and 0x21. The address of 0x20 is lower byte and 0x21 higher byte. The compiler will use the 7th bit of the byte with the address of 0x21 to replace this bit variable.

#### 5 Modules

Lumousft graphical language is specially designed for microprocessor application, the program consists of 5 parts:

- Main process module: It is similar to c language 'main' function, as shown in Fig.10 (a).Usually There is a big loop in embedded application, a terminal block named End Loop is introduced if necessary.

- Library: support compilation for logical and arithmetical operation

- Interruption: it is to handle interruption routine for microprocessor, as shown in Fig.10 (b).

- Sub module: it is similar to the function in c language and can be used by other modules. Sub modules can exist in different files. Sub module can be either module function or inline module as shown in Fig.10 (d) and (e).

- Global initialization: It is used to initialize global, system and static variable and perform microprocessor initialization before running main program module as shown in Fig.10 (c).

For the simplicity, we use single block to represent complex block networks in Fig.10.

A sub module in lumousoft graphical language is a group of blocks to achieve a special task, and at any point of statement in a block it can be called, just the same as function in textual language. Lumousoft graphical language treats the sub module name as a variable, while the function in textual language it is just a return value. In lumousoft graphical language, if a sub module name followed by a parentheses, it indicates that the sub module will be called and assign a return value to this sub module name variable. If there are not parentheses followed, the sub module is simply a variable.

Fig. 10. Modules

The sub module can be divided into two kinds of modules, inline sub module and regular sub module, just like inline function and function in textual language. Inline sub module means that the calling statement is completely replaced with the copy of the whole group of module blocks. A regular sub module is used to be called. Because sub module name is a variable, there is no need to be declared. But if the sub module is in another file, it needs to be imported. When the file is imported, all the sub-modules in the imported file can be implemented.

Since the main module and the interruption module belong to different thread, the memory of variables should be isolated except to that of global variable. If the different thread modules call the same sub module, Lumousoft graphical compiler will makes one copy of the sub module including variables for each thread usage.

#### 6 Assemble Language

Since assembly language is flexible and efficient, the assembly language is still found application in embedded field. Usually assembly language is embedded in other language.

Lumousoft graphical language allows assembly language to be embedded in block environment.

Assembly language operand can be a variable defined in the module including array, pointer except bit variable. But these variables used in assembly language must be those variables that have known address through static analysis. Unhandled variable like a[i], \*p, where p=&x+i; the variable "a" is array variable and "i" is a variable, "p" is pointer variable; in other words, these unhandled variables are those that are only handled by indirect address.

Because the assembly instruction only handles single- byte variable, if a variable is composed of more than one byte, only the first byte can be handled by assembly instruction. To solve one-byte problem, we can implement pointer to handle all bytes.

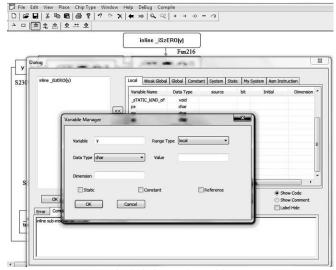

#### 7 IDE

Lumousoft IDE offers the facility to lay out lumousoft graphical program, compilation and generation of assembly codes, machine codes for burning to microprocessor as well as other files like block flow file which textually describes how the block flow, assignment file for variable address assignment and label of program memory address. Fig.11 shows the interface of IDE.

Lumousoft IDE graphical editor functions include drawing line, block, directions, and terminal block. The editor has functions like undo, redo, copy, delete, cut, paste, move, save, selection, search etc.

The codes in block are edited through block diagram, which pops up when double clicks on a block that wants to be edited. Fig.11 shows the block dialog and variable manager. The upper left text block is used to fill in codes. When a statement is put in, the IDE will perform lexical analysis and

Fig. 11. Block dialog and variable manager

obtain variable, key words and other tokens. The scanned variables are put into the variable tables on the right hand side. When IDE find a new variable, the variable has default attribute with data type of char and range type of local. The variable can be edited and change its attributes through variable manger dialog as shown in Fig.11. All the variables within the connected blocks can be accessed.

The bottom box is used for the user to write comment for this block. Codes and comments can be flipped to display by clicking on the radio button in the middle on the right hand side of block dialog.

Two situations need to be considered when click on "compile" button on the right top of the menu bar:

- The current file does not contain main module. When click on "compile", it will generate an object file with extent name "sub", which is used for other files to import.

- The current file contains main module. When click on "compile", it will generate assembly codes and machine codes for microprocessor.

#### 8 Examples

#### 8.1 Example 1

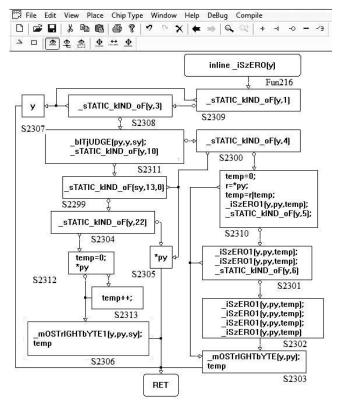

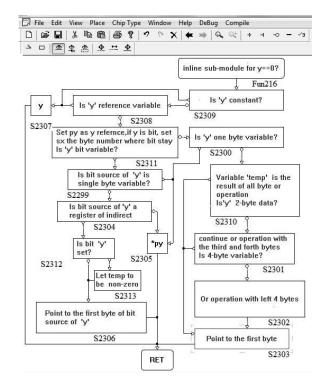

The example codes, shown in Fig.12, is an inline module from the Lumousoft library, which is used to judge whether the variable is zero for all kinds of data type such as bit variable, constant, pointer variable, one byte or multiple byte variable.

Fig. 12. An example graphical codes

Fig.13 is an alternative displays of code, showing the block comment to indicate how the program flow.

Fig. 13. Graphical pseudo codes

#### 8.2 Example 2

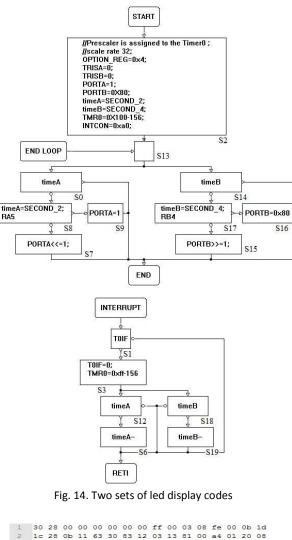

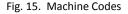

The next example is to design two sets of led display by use of PIC16F677. The port A connects to a set of led and the port B to another set of led. In each set of led, only one led lights up at each time, all the leds display in turn. For the first set, each led lights up for 2 seconds; while, for the second set, each led lights up for 4 seconds.Interuption takes place every one millisecond to record time. Since the two sets of led operate simutaneously, we can apply parallel to handle. Fig. 14 and Fig.15 illustrate the graphical codes and machine codes repectively.

#### 9 Conclusion

Lumousoft graphical language is a high-level graphical programming language, designed for microprocessor based embedded system, allowing the user to design and develop embedded software in the block environment. Lumousoft graphical language uses path analyzer to analyze block network connection pattern instead of parse tree, as a result, lumousoft graphical language can offer more flexible and intuitive method to handle more complicated algorithm with less efforts. Taking advantage of path analyzer, Lumousoft graphical language is able to determine each variable life span and make full recycle of memory. Lumousoft IDE offers the facility to layout lumousoft graphical program, compilation and generates assembly codes, machine codes. Lumousoft graphical language provides a graphical coding solution to handle embedded software engineering like other blueprints based engineering field. Because of graphical coding, lumousoft graphical language can give the user a bird view of their project with great convenience of embedded software maintenance, review, design, coding, validation, verification, test and modification.

a4 04 21 08 a4 04 03 1d 28 28 a4 01 22 08 a4 04 23 08 a4 04 03 1d 20 28 7e 08 83 00 7f 08 09 00 3 01 30 a2 02 03 1c 25 28 1c 28 01 30 a3 02 01 30 a0 02 03 1c 2d 28 15 28 01 30 a1 02 24 28 2c 28 04 30 83 16 03 13 81 00 85 01 86 01 01 30 83 12 85 00 80 30 86 00 d0 30 a2 00 07 30 a3 00 a0 30 a0 00 0f 30 a1 00 64 30 81 00 a0 30 8b 00 a5 01 22 08 a5 04 23 08 a5 04 03 1d 56 28 d0 30 a2 00 07 30 a3 00 85 1e 69 28 01 30 85 00 a5 01 20 08 04 21 08 a5 04 03 1d 65 28 a0 30 a0 00 a5 Of 30 a1 00 06 1e 66 28 80 30 86 00 47 28 03 10 86 0c 65 28 85 0d 05 10 56 28 00 00 00 00 00 00 00 00

#### **10 References**

[1] Bragg, S.D., Driskill, .G. D, "Diagrammatic-graphical programming languages and DoD-STD-2167A", AUTOTESTCON '94. IEEE Systems Readiness Technology Conference. 'Cost Effective Support Into the Next Century', Conference Proceedings, pp 211 - 220, Sep. 1994. [2] W.Ackerman, "Data Flow Languages", IEEE Computer, pp.15-25, February, 1982.

[3] Y. Zhang and B. Xu. "A survey of semantic description frameworks for programming languages". ACM SIGPLAN, 39(3):14–30, 2004.

[4] Charles N. Fischer, Richard J. LeBlance, Jr. "Crafting a Compiler", Benjamin-Cummings Publishing Co., Inc. Redwood City, CA, USA, 2010.

[5] Dick Grune, Herri E.Bal, Ceriel J.H. Jacobs and Koen G. Langendoen,"Modern Compiler Design", John Wiley & Sons, Inc., New York, NY, USA, 2000.

### Analysis and Optimization of *Paradigm* Microprograms

Victor L. Winter<sup>1</sup>, James McCoy<sup>2</sup>, Dominic Montoya<sup>3</sup>, and Greg Wickstrom<sup>4</sup>

<sup>1</sup>Department of Computer Science, University of Nebraska at Omaha, Omaha, NE, USA

<sup>2</sup>Sandia National Laboratories, Albuquerque, NM, USA

<sup>3</sup>Sandia National Laboratories, Albuquerque, NM, USA

<sup>4</sup>Sandia National Laboratories, Albuquerque, NM, USA

Abstract—Microcode often plays a key role in modern processor architectures. Microcode optimization is an important topic, and opportunities for microcode optimization can present themselves at various levels of abstraction. The Paradigm System, developed as part of a joint research effort between Sandia National Laboratories and the University of Nebraska at Omaha, consists of a high-level architectureindependent microprogramming language together with it's compiler. This paper discusses the artifacts and mechanisms, within the Paradigm System, that support the analysis and optimization of Paradigm microprograms.

**Keywords:** micro-programming, microprogram optimization, microprogram analysis, program transformation

#### 1. Introduction

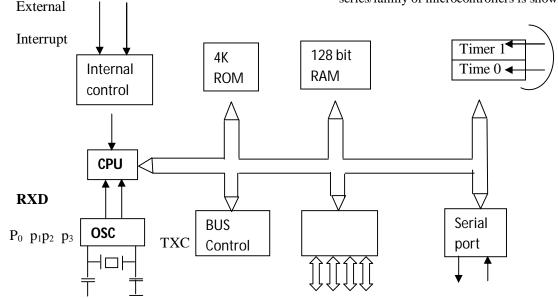

On modern processing platforms there oftentimes exists a computational gap between the functionality provided by the *assembly language instruction set*, which is targeted by high-level language compilers, and the set of *signals* used to control hardware resources. In such an environment, microcode ( $\mu code$ ) can be effectively used to emulate the functionality of assembly language instructions that are not directly supported by the hardware.

Because  $\mu code$  lies at the core of a processor's design, it's optimization is an important topic. Efficiency gains in  $\mu code$ , even small gains, can have a substantive impact on systemlevel performance. Research into the optimization of  $\mu code$  spans algorithmic optimization of high-level  $\mu code$  down to determining the optimal order in which microoperations ( $\mu operations$ ) should be executed.

#### 1.1 Application

$\mathcal{P}aradigm$  is a high-level architecture-independent microprogramming ( $\mu programming$ ) language that has been developed as part of a joint research effort, funded by Sandia National Laboratories (SNL), between SNL and the University of Nebraska at Omaha. The primary application motivating  $\mathcal{P}aradigm$  is the development of a processor, called the *Scalable Core* (*SCore*) [1]. The SCore is a hardware implementation of a subset of the JVM, designed and developed at SNL, for use in high-consequence embedded systems [2].

Within the SCore, the functionality of Java bytecodes is achieved through  $\mu programming$ . In particular, each Java bytecode supported by the SCore is realized through a corresponding  $\mu code$  implementation. Furthermore, native methods used in the JVM and supported by the SCore are also implemented in  $\mu code$ .

#### 1.2 Contribution

The  $\mathcal{P}aradigm$  System provides a unique environment for exploring  $\mu code$  optimization through a mixture of manual activities such as restructuring high-level  $\mu programs$  and automated activities such as the compaction of low-level  $\mu code$  performed by the  $\mathcal{P}aradigm$  compiler.

This article will discuss the following aspects of the Paradigm System that facilitate  $\mu code$  analysis and optimization.

- *extensive analysis* The *Paradigm* compiler produces a variety of artifacts (heat maps, graphs, tables) providing developers with insight into the allocation of registers that occur during compilation as well as detailed estimates of time/space trade-offs associated with calling versus in-lining methods.

- user defined optimizations  $\mathcal{P}aradigm$  developers can affect compilation in three important ways: (1) through *in-lining directives*, which are source-code level directives instructing the compiler to inline particular methods, (2) through *optimizing transformations*, which are transformation rules that developers can add to the compiler itself in order to perform specific optimizations during compilation, and (3) through *timing constraints*, which are used to guide the compaction of  $\mu code$  instructions.

The remainder of this article is structured as follows: Section 2 reviews some the basic concepts and terminology of microcoding. Section 3 overviews related work. Section 4 discusses analysis artifacts produced by the *Paradigm* compiler. Section 5 overviews user-defined optimization rules that can be added to the *Paradigm* compiler. Section 6 describes the declarative language used by *Paradigm* to specify parallel capabilities of a target machine, and Section 7 concludes.

#### 2. The Basics of Micro-programming

The purpose of  $\mu programming$  is to orchestrate the behavior of resources in a CPU. The basic concept was developed by Maurice Wilkes [3] in 1951 who also coined the term *micro-programming*. Microprogramming ( $\mu programming$ ) provides what amounts to a software-based alternative to the hardware-based logic boxes whose design was (and is) considered to be a bit of a black art[4].

A  $\mu program$  is a specification of how the resources within a CPU are to be controlled.  $\mu programs$  can be expressed at various levels of abstraction: *High-level*  $\mu programs$  strive to facilitate human comprehension, and can have syntactic and semantic similarities to high-level general-purpose programming languages such as C and Java. In contrast, *low-level*  $\mu programs$  are suitable for execution on a processor. The purpose of a  $\mu compiler$  is to translate a high-level  $\mu program$ into a low-level  $\mu program$ .

A low-level  $\mu program$  consists of a sequence of  $\mu instructions$ . A  $\mu instruction$  consists of a set of  $\mu operations$  each of which specify the control of a fundamental resource within the processor. Typical examples of  $\mu operations$  include:

- the transfer of data from memory to a register

- elementary operations such as shift, load, and clear performed on data residing a register

- properly updating the internal registers of the control unit in order to enable a jump

A *µoperation* consists of a set of *fields*. Fields are made up of bits whose binary values correspond to control lines. For example, a field consisting of k bits can be used to denote  $2^k$  combinations of control lines. A special case arises when k = 1 for all fields. *µinstructions* constructed exclusively from *µoperations* having 1-bit fields are referred to as *horizontal µinstructions*. Horizontal *µinstructions* are long, but allow for the maximal expression of parallelism. In contrast, the signals denoted by fields for which k >1 are encoded, and *µinstructions* made up of such fields are referred to as *vertical µinstructions*. A benefit of such encoding is that the bit-width of *µinstructions* is significantly reduced. However, the parallelism which can be expressed through vertical *µinstructions* is limited and combinatory logic is needed to decode field values.

Orthogonal to the vertical/horizontal nature of a  $\mu$ *instruction* is the architectural notion of how many  $\mu$ *operations* a  $\mu$ *instruction* can hold. If only a "few"  $\mu$ *operations* can be placed into a  $\mu$ *instruction* the machine has a *vertical architecture*; otherwise it has a *horizontal architecture*[5][6].

For architectures that support concurrent execution of  $\mu operations$ , be they vertical architectures or horizontal architectures, the scheduling of  $\mu operations$  presents an area of optimization. In this context, the goal of optimization is to produce a low-level  $\mu program$  having a minimal or

near-minimal number or  $\mu$ instructions. For this form of optimization, referred to as  $\mu$ code compaction, achieving optimal results has been shown to be NP-complete[7]. There are two types of compaction: (1) local compaction which focuses on restructuring the  $\mu$ operations within straight-line  $\mu$ code(SLM) – also known as basic blocks, and (2) global compaction whose focus spans multiple SLMs.

#### 3. Related Work

Research into the design of high-level  $\mu programming$ languages and  $\mu compilers$  predominantly took place during the 1970's and early 1980's. A number of papers have been published on the topic of  $\mu code$  optimization [8], [9], [10], [5]. Agerwala [11] has written a survey on  $\mu code$ optimization. A central issue in the type of optimization discussed in the survey is the reduction of the size of the *control memory* needed to hold a  $\mu program$  implementing a given function. Here, the control memory is modeled as a two-dimensional array ( $W \times B$ ) where W denotes the number of words (i.e., rows) and B denotes the number of bits (i.e., columns) in the control memory respectively. A primary goal of optimization is to reduce the control memory along either of its dimensions.

In [11], optimization strategies are categorized as being either high-level or low-level. High-level optimizations are based on dataflow analysis of the source-code and strive to discover parallelism inherent in the algorithm implementation. Optimizations possible at this level also include existing (well-known) compiler optimization techniques. Roughly stated, the result of high-level optimization is a sequence of sets, called *time frames*, whose elements are *µoperations*. This sequence of time frames is viewed as partitioning the computation defined by the high-level (input) *µprogram* in a manner that is maximally parallel irrespective of physical limitations of the host machine. After such a partitioning has been completed, low-level optimizations can be applied to map the structure onto a host machine. These low-level optimizations center on normalizing the existing partition structure so that each set in the partition can be realized by exactly one horizontal *µinstruction*.

SIMPL (Single Identity Microprogramming Language) [12] is a high-level (machine dependent)  $\mu programming$  language developed in the early 70's having an ALGOL-like syntax. During SIMPL compilation, a high-level *sequential program* undergoes sophisticated analysis in order to produce a highly optimized low-level *horizontal program*. SIMPL optimization is based heavily on the *single identity principle* which states that a (particular) definition for a variable holds from the point it is assigned up to the point where it is reassigned. The single identity principle forms the basis for partitioning a sequence of statements into *subblocks* each of which constitute an independent set of  $\mu operations$ . This decomposition represents a key first step in solving the global optimization problem.

Though there were a number of  $\mu code$  language and compiler development efforts underway at the time, SIMPL was considered to be the first high-level  $\mu programming$  language in which both compilation and optimization were performed automatically. A SIMPL compiler has been developed targeting the Tucker-Flynn dynamic microprocessor [13].

Micro-C [14] is a high-level machine-independent  $\mu programming$  language compatible with C. A Micro-C  $\mu program$  can be compiled by a special compiler based on the Portable C Compiler. The output produced by this compiler is vertical (i.e., unoptimized) symbolic  $\mu code$ . This intermediate representation can then be optimized by a "straight-line" *packer* which translates sequences of  $\mu operations$  into horizontal  $\mu instructions$ . An assembler is then used to translate the result into executable low-level  $\mu code$ .

In [15], a language is presented in which high-level  $\mu programs$  are composed of *declaration* statements and *command* statements. The compiler for this language consists of two phases: In the first phase of compilation, the input  $\mu program$  is parsed, analyzed, and an unoptimized sequence of  $\mu instructions$  is produced. At this stage, each  $\mu$ -instruction performs exactly one *elementary operation* (i.e., a  $\mu operation$ ). The second phase of compilation is an optimization phase in which a number of tables containing machine-dependent information (e.g., parallel capabilities of the hardware) are employed in order to *compact*  $\mu instructions$  taking full advantage of the parallel capabilities of the hardware.

In [16], an approach is presented where machineindependent high-level  $\mu code$  optimization is performed by the software component of a  $\mu code$  compiler and low-level machine-dependent optimization is performed by hardware residing on the host machine (i.e., the machine on which the  $\mu code$  will be executed). In this context, the goal of a hardware microcode optimizer(HMO) is to condense a sequence of  $\mu$ instructions (i.e., where each  $\mu$ instruction contains only one  $\mu$ operation) into a functionally equivalent sequence of  $\mu$ *instructions* taking full advantage of the parallel capabilities of the host machine. At a higher-level, optimization strategies are divided into two distinct categories: The local optimization category is performed by the hardwarebased component of the compiler and focuses on the serial combination (i.e., compaction) of  $\mu$ instructions. The global optimization category is performed by the software-based component of the compiler and focuses on the commutative reordering *µinstruction* sequences (driven by dataflow analysis) in order to more fully exploit parallelism.

#### 4. Analysis

In addition to designing well-structured high-level  $\mu$ *programs*, developers often need to pay close attention to the consumption of resources entailed by their design. For

example, how many internal registers are needed by the compiler to compile a given high-level  $\mu program$ ? What is the size, in terms of the number of  $\mu instructions$ , of the resulting low-level  $\mu program$  produced by the compiler? And, how many  $\mu instructions$  are executed when the program is run?

The  $\mathcal{P}aradigm$  compiler produces three artifacts to assist developers in their optimization-oriented analysis efforts: (1) views, (2) heat maps, and (3) estimation tables.

#### 4.1 Views

*Paradigm* provides a notation, called a *view*, for specifying subsets of methods. From the specification of such subsets, views can be constructed. In particular, a view is an acyclic directed graph whose nodes denote methods and whose labeled edges denote the number of internal registers allocated by the compiler relative to specific nodes. For example, consider the graph below consisting of two nodes, labeled *f* and *g*, connected by an edge labeled 12.

This graph indicates that (1) the method g is called in the body of f, and (2) at the point of the call to g, the compiler has allocated 12 internal registers local to the context of f.

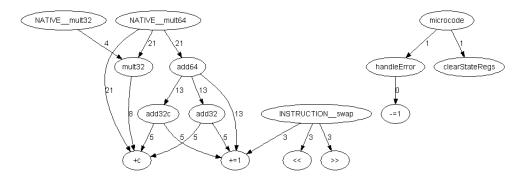

A high-level  $\mu program$  may have multiple views defined for it, each of which will be output to a correspondingly named file. Such files are output in a "dot format" and can be viewed using Graphviz. Figure 1, shows an example of a view generated by the *Paradigm* compiler for a  $\mu program$ produced for a hypothetical machine.

#### 4.2 Heat Maps

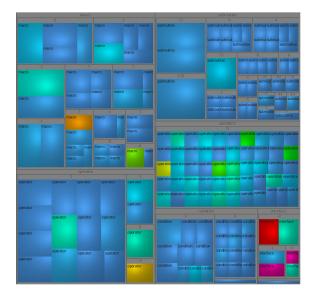

Heat maps are another form of feedback produced by the *Paradigm* compiler. Specifically, the *Paradigm* compiler will output twelve attributes to a file in a comma-separated value format. Attributes range from method arity, method size, reference frequency, inlined - called size, to (inlined called size) \* reference\_frequency. Figure 2 shows a heat map for a hypothetical machine. In this heat map, the first grouping (in grey) is by method type (e.g., macro, subroutine, operator, operation, condition, interface). The second grouping (also in grey) is the difference between the in-lined size and the called size - this includes all overhead associated with making a method call. The size of squares in the heat map represents the called size, and the color indicates reference frequency with red denoting the most frequently referenced methods and blue denoting the least frequently referenced methods.

#### 4.3 Efficiency Estimator

In order to meet resource constraints, it may be necessary for developers to optimize their high-level  $\mu program$ . To facilitate optimization,  $\mathcal{P}aradigm$  provides high-level language directives that can be used to instruct the compiler to in-line various method declarations.

Fig. 1: A view showing internal register allocations performed by the compiler.

Fig. 2: Heat map of  $\mu code$  for a hypothetical machine.

Method in-lining represents a time/space tradeoff, since in-lining can cause the size of the low-level  $\mu code$  to expand dramatically. For example, suppose the body of a method m consists of 100 lines of  $\mu code$ . Further suppose that mis called in 10 places in the  $\mu code$ . If all 10 calls are inlined, then in-lining (without compression) will yield 1000  $\mu instructions$ . In contrast, suppose that a *call* to the method m requires 20 lines of  $\mu code$ . In this case, calling m 10 times will result in a total overhead of 200 lines of  $\mu code$ . Thus, an implementation in which m is called will contain 700 fewer lines of  $\mu code$ (i.e., 200 lines of call overhead plus 100 lines for the method body). However, it should be noted that in-lined methods always execute faster than their called counterparts since there is no call overhead associated with their execution.

The overhead associated with a method call is significant. Internal registers must be allocated for the input parameters. Instructions must be generated by the compiler to *move* actual parameters to the internal registers corresponding to formal input parameters of the method. A *call* instruction must be generated by the compiler to transfer execution to the method body, and a *return* must be executed upon completion of the method body. Furthermore, moves, calls, and returns do not lend themselves to compression. In other words, only one such  $\mu$ operation will fit into a  $\mu$ instruction. Thus, going back to our previous example, if the execution of each  $\mu$ instruction takes 1 unit of time, then executing the body of m via a call will take 120 units of time.

As the body of a method gets smaller it gradually becomes more attractive to in-line a method. Eventually, a crossover point is reached where calling a method consumes more time and more space than simply in-lining a method. It should be noted that, from the point of view of development, the method is a mechanism for abstracting functionality. Thus, a best-practices approach to development would encourage the use of methods as needed to give clarity to an implementation.

The *Paradigm* compiler, provides an estimation of the effects of method call versus method in-lining. In particular, two sorted tables are produced: (1) a *static call-frequency estimation table*, and (2) an *execution path estimation table*. Examples describing the information in both of these tables are described in the sections that follow.

#### 4.3.1 Example: Static Call-Frequency Estimation

Suppose method m1 is an in-line method candidate having 3 formal input parameters. Furthermore, let us assume that a static inspection of the *Paradigm* application reveals that m1 is called from 10 syntactically distinct locations. Similarly, suppose method m2 is inline candidate method having 2 formal input parameters. Furthermore, let us assume that a static inspection of the *Paradigm* application reveals that m2 is called from 20 syntactically distinct locations.

| Static | <b>Call-Frequency</b> | Estimation |

|--------|-----------------------|------------|

|--------|-----------------------|------------|

|        | State Gan Frequency Estimation |                     |  |  |  |

|--------|--------------------------------|---------------------|--|--|--|

| Method | Move Instruction Overhead      | Static Overhead Sum |  |  |  |

| m1     | 3 * 10 = 30                    | (3+2) * 10 = 50     |  |  |  |

| m2     | 2 * 20 = 40                    | (2+2) * 20 = 80     |  |  |  |

It should be noted that static-call-estimation provides a fairly course grained and basic estimation of the overhead associated with calling methods. In particular, static call estimation does not take into account execution paths which can have multiplicative effect on the number of times a method can actually be called during runtime. For example, suppose method m1 is called twice in the body of method m2, and suppose method m2 is called 5 times within the  $\mu code$ . Note that in this example, there are only 2 lexical occurrences of m1. However, m1 will be called a total of 5 \* 2 = 10 times during the execution of the application. We call this second form of estimation execution path estimation. It should be noted that, since it does not account for loop iterations, execution path estimation is also only an estimate, albeit a more accurate one than static call estimation.

#### 4.3.2 Example: Execution Path Estimation

Suppose methods m1, m2 and m3 are respectively called 5, 6, and 4 times from the  $\mu code$  as shown in Figure 3. Also note, that m1 is called 2 times from m2 and m2 is called 3 times from m3.

The execution path estimation table shows that the total calls for m1 is 41. This value corresponds to the sum: 1 \* 5 + 1 \* 6 \* 2 + 1 \* 4 \* 3 \* 2 = 41. More specifically, m1 is called 5 times from the  $\mu code$ . This accounts for the 1 \* 5 term. Next, m1 is called 2 times from m2, which itself is called 6 times from the  $\mu code$ . This accounts for the term 1 \* 6 \* 2. And finally, m2 is called 3 times from m3 which is called 4 times from the  $\mu code$ . This accounts for the term 1 \* 4 \* 3 \* 2.

In this example, the in-lined size for m1 is 0. This is because the body of m1 is empty (after the removal of the return instruction). The called size for m1 is 83 and corresponds to 41 calls plus 41 returns plus the size of the declaration of m1 (which is 1).

The in-lined time will always be equal to the in-lined size. The assumption here is that each row in the  $\mu code$  takes 1 unit of time to execute, and that additional compression of method bodies is not possible.

The called time for m1 is 82. This corresponds to the total calls to m1 times the sum of the number of moves associated with calling m1 plus the number of microcode rows associated with the call-to and return-from m1.

And finally, the speed up is 100%. This number is computed using the following formula:

# $\begin{array}{c} 100.0-\\(inlined\_execution\_time/called\_execution\_time)*\\ 100.00\end{array}$

Although it is not highlighted by the example given, it should be noted that the execution path estimator accounts for the mandatory inlining of all *macros*, *interfaces* and

|        |          |     |      | Siz | <i>e</i> |

|--------|----------|-----|------|-----|----------|

| Method | Total Ca | lls | Inli | ned | Called   |

| m1     |          | 41  |      | 0   | 83       |

| m2     |          | 18  |      | 36  | 39       |

| m3     |          | 4   |      | 12  | 12       |

|        | Tir      | ne  |      |     |          |

| Method | Inlined  | Ca  | lled | %   | Speedup  |

| m1     | 0        |     | 82   |     | 100%     |

| m2     | 36       |     | 72   |     | 50.0%    |

| m3     | 12       |     | 20   |     | 40.0%    |

Table 1: Execution path estimation.

```

interface call(LabelType toLabel) { aux_call(); }

interface return() { aux_return(); }

subroutine m1() returns void { return(); }

subroutine m2() returns void {

m1(); m1(); return();

}

subroutine m3() returns void {

m2(); m2(); m2(); return();

}

microcode {

m1(); m1(); m1(); m1(); m1();

m2(); m2(); m2(); m2(); m2();

m3(); m3(); m3();

}

```

Fig. 3: Example used for execution path estimation

*conditions*<sup>1</sup>. This is important because such mandatory inlining can result in dramatic changes in the final size of a subroutine or operator. Also note that the size of the call and return interfaces also take inlining into account.

#### 5. User-defined Optimization Rules

The *Paradigm* compiler is transformation-based and implemented in the TL System[17]. During compilation, a *Paradigm* program is passed through a number of canonical forms, each of which can be output in human-readable form. The *Paradigm* compiler is *extensible* in the sense that it supports the incorporation of user-defined transformation rules into the compilation process. Such rules provide domain experts the opportunity to perform custom optimizations specific to a particular architecture or  $\mu code$  design. Figure 4 is an example of a  $\mu code$  fragment, which can be output by the compiler, consisting of a sequence of  $\mu operation$  method calls separated by labels denoting jump destinations (e.g., starting positions of methods whose bodies have not been in-lined).

By inspection of the sequence of operations we see that a *writeReg* operation is immediately followed by a *copyReg* operation. Suppose that by combining knowledge of the

<sup>1</sup>The language  $\mathcal{P}aradigm$  has five different kinds of methods. The rational behind this is beyond the scope of this article.

| label_f:              |           |               |

|-----------------------|-----------|---------------|

| writeReg(T1Type.SOM   | AType.\$t | emp_reg 3);   |

| copyReg( AType.\$tem] | reg 3 ,AT | ype.\$reg 2); |

Fig. 4: A  $\mu code$  fragment prior to custom optimization.

hardware architecture together with our understanding of the semantics of the implementations of the *writeReg* and *copyReg* operations we conclude that the transformation shown in Figure 5 is correctness-preserving. Furthermore, suppose that additional analysis leads us to conclude that such a transformation would be correctness-preserving **in all contexts**. That is, regardless of how it gets generated by the compiler, whenever a "write" to a temp register X is followed by a "copy" from that temp register X to the register Y, then this pair of operations can be replaced by a single operation that will directly "write" to the register Y.

Given that these conditions hold, we would like to expand the functionality of the compiler to include such an optimizing transformation.  $\mathcal{P}aradigm$  supports such extension of its compiler through a special transformation module in which domain experts can place custom-designed program transformations. There are no restrictions on the nature of the transformations that can be created. In particular, optimizing transformations can be developed utilizing the full capabilities of the TL system.

```

writeReg(TlType.SOME, AType.$temp_reg 3);

copyReg(AType.$temp_reg 3, AType.$reg 2);

→

writeReg(TlType.SOME,AType.$reg 2);

```

Fig. 5: A custom program transformation.

# 6. *Paradigm*'s Timing Constraint Language

*Paradigm* provides a declarative language, called TCL, for specifying the timing constraints of a targeted hardware architecture. Timing constraints form the basis of a *local compaction* algorithm focusing on the compression of straight-line  $\mu code$  (SLM). Timing-constraint based optimization does not involve commutative reordering of  $\mu operations$ , instead it focuses on maximizing the compression of adjacent (i.e., associative)  $\mu instructions$ . It is worth mentioning that in the compilation stage where timing-constraint based optimization occurs, the  $\mu program$  being compiled is in a form where all non-sequential control flows are expressed in terms of jumps to labels. In this context, an

SLM is then simply the sequence of  $\mu$ *instructions* occurring between consecutive labels.

Conceptually, a timing constraint is a pair of logical formulas that, if satisfied by adjacent  $\mu$ instructions, prevent them from being compressed into a single  $\mu$ instruction. Compression is also (implicitly) prohibited in cases when corresponding fields, in adjacent  $\mu$ instructions, contain distinct (i.e., unequal) non-default signals.

An abstract example of the syntax of a timing constraint is shown in Figure 6. In the example,  $\mathcal{F}_1$  and  $\mathcal{F}_2$  denote the pair of logical formulas of the timing constraint named  $TC_k$ .

The evaluation of  $TC_k$  with respect to a pair of adjacent  $\mu$ *instructions*  $\mathcal{I}_j$  and  $\mathcal{I}_{j+1}$  proceeds as follows: If  $\mathcal{I}_j$  satisfies  $\mathcal{F}_1$  and  $\mathcal{I}_{j+1}$  satisfies  $\mathcal{F}_2$ , then we say that the the  $\mu$ *instructions*  $\mathcal{I}_j$  and  $\mathcal{I}_{j+1}$  satisfy the timing constraint  $TC_k$ , in which case the compression of  $\mathcal{I}_j$  and  $\mathcal{I}_{j+1}$  is prohibited by  $TC_k$ ; otherwise compression is not prohibited by  $TC_k$ .

| constraint $TC_k$ {                                           |  |

|---------------------------------------------------------------|--|

| first_row: $\mathcal{F}_1$ ;<br>second_row: $\mathcal{F}_2$ ; |  |

Fig. 6: An abstract example of a timing constraint.

TCL allows  $\mu code$  compression to be restricted by a *set* of timing constraints  $S_{TC} = \{TC_1, \ldots, TC_m\}$ . The compression of any pair of  $\mu instructions \mathcal{I}_j$  and  $\mathcal{I}_{j+1}$  is prohibited if  $\exists TC_k \in S_{TC}$  such that  $TC_k$  is satisfied by the  $\mu instructions \mathcal{I}_j$  and  $\mathcal{I}_{j+1}$ .

A more detailed look at timing constraints reveals that they are logical formulas, in conjunctive normal form, whose elements are equality/inequality matching-based comparisons involving fields. An abstract example of a disjunction constraining the fields f1 and f2 is shown below.

field.f1 = field1Type.item1 | field.f2 != field2Type.item2

Within an element, there are three kinds of *items* that can be associated with a fieldtype: (1) a *symbolic name* denoting a constant value belonging to a type declaration, (2) a *subscripted variable* which can match with field constants (occurring in the  $\mu$ *instructions* in which evaluation is taking place), and (3) the keyword DEFAULT/NONDEFAULT. The scope of a subscripted variable spans an entire constraint (both formulas) and can therefore be used to express equality-based properties between fields within a constraint.

The  $\mathcal{P}aradigm$  compiler provides feedback summarizing the impact of the optimizations it performs. Figure 2 shows an example of an optimization summary.

#### 7. Conclusion

In the design of a high-level architecture-independent  $\mu$  programming language, a major issue that must be confronted centers on how architecture-specific information can Optimization Metrics: Standard Compiler Optimizations. Total number of temp register optimizations = 0 Number of nop() statements removed = 0

Custom Optimizations.

Total number of row reductions due to custom optimizations = 0

Constraint-based Optimizations.

Number of row mergings prevented due to timing constraints = 1291 Number of duplicate row mergings = 500 Number of conflict-free row mergings = 1000

Total number of constraint-based row mergings = 1500

Total humber of constraint based for mergings = 13

Number of rows before any optimization = 2800

Number of rows after all optimization = 1300

Size of optimized file as a percentage of the unoptimized file = 46.43%The size of the unoptimized file was reduced by = 53.57%

Table 2: Optimization feedback provided by the *Paradigm* compiler.

be specified, as well as how the compiler for the language can utilize this information to produce efficient low-level  $\mu code$  targeting a host machine. Addressing this issue, Paradigm provides a timing constraint language (TCL) for specifying the parallel capabilities of a host machine. Furthermore, the *Paradigm* compiler also provides extensive feedback on the nature of its compilation, including pretty-printed representations of the program being compiled during various stages of compilation, register usage, call frequency, and comparisons between overheads associated with method call versus method in-lining. This information can be used to guide time/space optimizations involving design level decisions such as method in-lining and can even guide the development of user-defined rule-based application-specific optimizations that can be folded into the compilation process itself.

#### References

- J. A. McCoy, "An Embedded System For Safe, Secure And Reliable Execution of High Consequence Software," in *Proceedings of the* 5<sup>th</sup> IEEE International Symposium on High Assurance Systems Engineering (HASE). IEEE, 2000, pp. 107–114.

- [2] V. L. Winter, H. Siy, J. McCoy, B. Farkas, G. Wickstrom, D. Demming, J. Perry, and S. Srinivasan, "Incorporating Standard Java Libraries into the Design of Embedded Systems," in *Java in Academia* and Research, K. Cai, Ed. iConcept Press, 2011.

- [3] M. V. Wilkes, "The early british computer conferences," M. Campbell-Kelly, Ed. Cambridge, MA, USA: MIT Press, 1989, ch. The Best Way to Design an Automatic Calculating Machine, pp. 182–184. [Online]. Available: http://dl.acm.org/citation.cfm?id=94938.94976

- [4] R. C. Haavind, Jr, "The many faces of microprogramming: What started out as a convenience for systems designers may eventually bring computers much better tailored to users' needs," *SIGMICRO Newsl.*, vol. 2, no. 4, pp. 12–16, Jan. 1972. [Online]. Available: http://doi.acm.org/10.1145/1316527.1316529

- [5] D. Landskov, S. Davidson, B. Shriver, and P. W. Mallett, "Local microcode compaction techniques," ACM Comput. Surv., vol. 12, no. 3, pp. 261–294, Sept. 1980. [Online]. Available: http://doi.acm.org/10.1145/356819.356822

- [6] S. Dasgupta, "The organization of microprogram stores," ACM Comput. Surv., vol. 11, no. 1, pp. 39–65, Mar. 1979. [Online]. Available: http://doi.acm.org/10.1145/356757.356761

- [7] S. S. Yau, A. C. Schowe, and M. Tsuchiya, "On storage optimization of horizontal microprograms," in *Conference Record of the 7th Annual Workshop on Microprogramming*, ser. MICRO 7. New York, NY, USA: ACM, 1974, pp. 98–106. [Online]. Available: http://doi.acm.org/10.1145/800118.803848

- [8] J. Fisher, "Trace Scheduling: A Technique for Global Microcode Compaction," *Computers, IEEE Transactions on*, vol. C-30, no. 7, pp. 478–490, July 1981.

- [9] S. Davidson, D. Landskov, B. Shriver, and P. Mallett, "Some Experiments in Local Microcode Compaction for Horizontal Machines," *Computers, IEEE Transactions on*, vol. C-30, no. 7, pp. 460–477, July 1981.

- [10] P. Marwedel, "A Retargetable Compiler for a High-Level Microprogramming Language," *SIGMICRO Newsl.*, vol. 15, no. 4, pp. 267–274, 1984.

- [11] T. Agerwala, "Microprogram Optimization: A Survey," Computers, IEEE Transactions on, vol. C-25, no. 10, pp. 962–973, Oct. 1976.

- [12] C. Ramamoorthy and M. Tsuchiya, "A High-Level Language for Horizontal Microprogramming," *Computers, IEEE Transactions on*, vol. C-23, no. 8, pp. 791–801, Aug. 1974.

- [13] A. B. Tucker and M. J. Flynn, "Dynamic microprogramming: Processor organization and programming," *Commun. ACM*, vol. 14, no. 4, pp. 240–250, Apr. 1971. [Online]. Available: http://doi.acm. org/10.1145/362575.362580

- [14] W. C. Hopkins, M. J. Horton, and C. S. Arnold, "Target-Independent High-Level Microprogramming," in *MICRO 18: Proceedings of the 18th annual workshop on Microprogramming*. New York, NY, USA: ACM, 1985, pp. 137–144.

- [15] A. K. Tirrell, "A Study of the Application of Compiler Techniques to the Generation of Micro-code," in *Proceedings of the meeting on SIGPLAN/SIGMICRO interface*. New York, NY, USA: ACM, 1973, pp. 67–85.

- [16] J. O. Bondi and P. D. Stigall, "Designing HMO, an Integrated Hardware Microcode Optimizer," in *MICRO 7: Conference record* of the 7th annual workshop on Microprogramming. New York, NY, USA: ACM, 1974, pp. 268–276.

- [17] V. L. Winter, "Stack-based Strategic Control," in Preproceedings of the Seventh International Workshop on Reduction Strategies in Rewriting and Programming, June 2007.

#### **Rift Runner – Engineering Software for a Remotely Controlled Rover**

Erik Willis, Sean Saunders, Nathan Cate, Jean-Paul Muyshondt and Devon M. Simmonds,

University of North Carolina Wilmington, 601 S. College Rd. 601 South College Road, Wilmington, North Carolina, 28403 { emw8872, Sean\_saunders@outlook.com, nathanc\_ii@yahoo.com, jm5904, simmondsd }@uncw.edu

#### Abstract

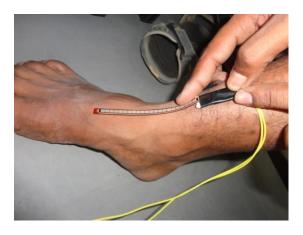

The Runner is a project based on the first-person piloting of a remotely controlled rover. The rover is controlled by an Oculus Rift, a 3d immersive headset that is designed to bring users into a deep experience of the piloting and manipulation of the vehicle. Users have the ability to upload and share their experiences through the team's web server. This paper describes a model-based approach to the project design along with results and lessons learned.

Keywords: software engineering, model driven engineering, embedded software, UML, Remotely controlled vehicle.

#### 1. Introduction

There is an entire world of radio-controlled (RC) vehicle enthusiasts that spend exorbitant sums of time and money on this exciting hobby. Entry-level cars start around \$120, planes from \$250 - \$300, but some planes can cost as much as \$20,000[1]. Until recently, piloting an RC vehicle has been a relatively static experience - stand in a field and watch the vehicle from a distance. As technology has progressed the dream of piloting an RC vehicle from a first-person perspective has become a reality. While the technology currently exists to pilot RC vehicles through video equipment relaying an image to a monitor, the military uses such technology to pilot drones and the market has been ripe for an affordable, first-person, 3-D version. As of 2009 there were more than 5300 aerial drones and 12,000 ground based drones [2]. The MQ-1 Predator Drone costs around \$4 million per unit [3], and the MQ-9 Reaper Drone costs upwards of \$12 million per unit [3]. Enter the Oculus Rift.

The Oculus Rift is a 3-D, immersive, virtual reality (VR) headset that is currently being coupled with video games to present a completely unique and

affordable user experience. The goal of this project is to combine a video camera equipped RC vehicle with the Oculus Rift to create an exhilarating piloting experience. While most of the drone technology is based around military uses, there are also non-military applications. The Miami-Dade County police department, for example, tested an aerial drone in 2011 with the aim of using the drone for aerial reconnaissance and suspect trailing [4]. Another drone that is non-military is the Curiosity Rover. On August 6, 2012 the Mars rover Curiosity landed on the red planet. Curiosity is scheduled to spend two years exploring Mars [5]. Our project is not intended for such serious endeavors, but simply to create entertainment value.

The Rift Runner is a project designed to enable the first-person piloting of a remotely controlled rover. Our main objective was to create a fun, usable, affordable piloting experience. The rover is controlled by an Oculus Rift, a 3d immersive headset that is designed to bring users into a deep piloting and manipulating experience of the vehicle. Vehicular control is achieved through the use of a gamepad while the Oculus Rift controls camera motion through the users head movements.

Our biggest initial concern was the extent to which we could successfully marry our various hardware solutions into a realizable platform. During initial research we discovered that video feed latency has been a problem for similar endeavors. As such we designed our hardware solution to minimize this latency and create a pleasant user experience. To go along with the vehicle we also created a web site that provides a view of the video feed and enables image captures and video segments to be saved. A database was also implemented to track user profiles and links to the image and video storage.

#### 2. Background

#### 2.1 Oculus Rift

The Oculus Rift is a virtual reality head mounted display (HMD) currently in development by Oculus VR. The device began when Palmer Luckey, a homeschooled tinkerer, decided to build his own virtual reality headset [6]. The project was originally debuted at the Electronic Entertainment Expo in 2012. John Carmack, cofounder of id Software and creator of the DOOM series, introduced the first prototype of the Oculus HMD [7]. Following the initial reveal at the E3 in June 2012 the company announced a Kickstarter campaign to raise funds to continue development of the Oculus Rift. After only four hours the company had secured its initial goal of \$250,000 and within thirtysix hours had raised more than \$1 million [8]. The Kickstarter campaign would later end having raised \$2,437,429 [9]. This funding was used to finance a developer's kit of the Oculus Rift. This developer's kit gave people early access to a reduced quality version of the final Oculus Rift but allowed game designers and other developers to begin creating and experimenting with virtual reality environments much sooner [10].

The Oculus Rift, or OR, simulates a purely visual experience for the user in their chosen environment. As a binocular HMD it is worn on the users head and features an optic display in front of each eye. The HMD fully encompasses the user's field of view ensuring as immersive an experience as possible. The OR uses a series of 3-axis gyroscopes, magnetometers, and accelerometers to make head orientation tracking nearly absolute in relation to the Earth. The gyroscopes track the angle of motion as the user moves their head; the accelerometers measure how quickly the HMD is moving; the magnetometers measure the gravitational pull of the Earth allowing the Oculus Rift to keep track of its own orientation with respect to "Up" and "Down" [11]. This head motion tracking is translated to the screen inside the HMD: when the user turns their head to the left the view turns with them. This feature combined with a 90 degree field of view creates a visual experience that mimics real life. Using the Oculus Rift is so immersive and fluid that many users have reported having motion sickness after less than a minute of use. This is caused by the mind thinking the body is moving but in reality the body remains stationary. This issue has been addressed by the company in a recent press release by Oculus VR CEO Brendon Iribe in which he states "It is going to work...It's gonna work for everybody." A reduction in screen shaking and latency has improved

this aspect of the experience for users [12]. These updates won't be seen in the Oculus Rift until the release of the second Developer's kit. The currently available developer's kit still suffers from these motion sickness inducing problems.

#### 2.2 Virtual Reality

Virtual reality is a computer-simulated setting that can generate an artificial physical presence either in the real world or abstract environments. Virtual reality can trace its lineage back to the 1500's when artists would create 360 panoramic scenes that would take up entire rooms. An example of this is the Sala delle Prospettive, a work by Italian painter Baldassare Peruzzi [13]. It was not until 1966 that the world saw its first glimpse of virtual reality when the T-27 Space Flight Simulator was created for the U.S. Air Force Aerospace program. The simulator was designed to train pilots for space research missions [14]. In 1991 MIT graduate and NASA scientist Antonio Medina developed a system to help direct Mars robots from Earth. This system is an extension of virtual reality [15]. Until recently the technology for virtual reality has been limited in quality or availability for the general public. The Oculus Rift aims to change that.

#### 3. Software Design

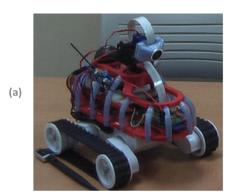

Figure 1. (a) Rift Runner Rover, (b) Oculus Rift and Controller

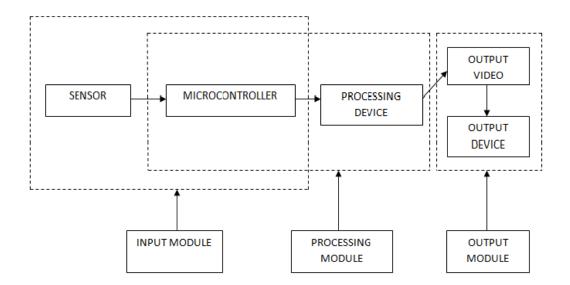

In this project, hardware architecture preceded software architecture and consisted of the rover (Figure 1a), and the Oculus Rift and controller (Figure 1b). As Figure 1a shows, the camera is mounted at the top and front of the rover.

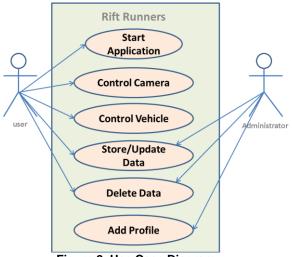

Figure 2. Use Case Diagram

The Rift Runner software was designed using a Model-Driven approach [19-21]. The design includes UML [22] use case diagram (See Figure 2), UML activity diagrams (see Figure 3), an architectural diagram (see Figure 3), and Class diagram (see Figure 4).

The Use Case Diagram (Figure 2) illustrates typical actor interaction with the Rift Runner software and rover. Actors include the end User and the systems administrator who has exclusive rights to add and delete user profiles.

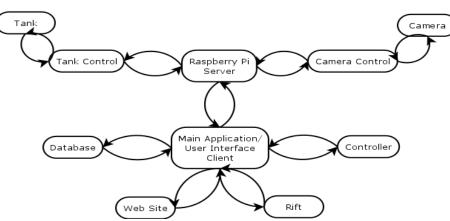

#### 2.1. Architectural Design

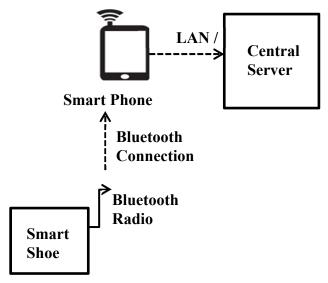

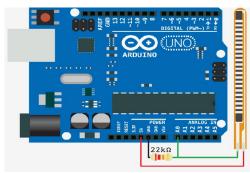

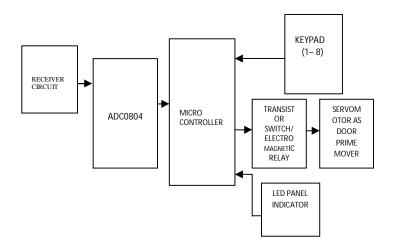

The physical architecture for this project consisted of the tripartite configuration of (1) the rover and Raspberry Pi, (2) the Oculus Rift and (3) the computer running the software. The logical architecture consisted of a client-Server model centered around a single UDP server as depicted in Figure 5. The UDP server exists on the Raspberry Pi and is responsible for pushing all the data from the main application to the correct hardware, as well as feeding the image data from the camera to the main application. The Raspberry has Pi limited computability having only 512 Mb of RAM, therefore all of the number crunching is done in the main application and then fed to the Raspberry Pi through

the UDP link. UDP offers a fast connection, a requirement to limit image lag in the OR, but has no guarantee of message integrity. Since the application is pulling information from the various input devices at a rate of 50 times a second a few misplaced packets is not mission critical.

The UDP client class packetizes all data from the main application before passing it to the UDP server. The main benefit of this architecture is that with our implementation there is a single link of communication. All data passes from the main application through the client to the server and from there to the correct hardware. The fast data transport enabled by this single, simple communication link helps to keep the latency to a minimum. While the simplicity of this link is a major asset, the fact that it is solitary (with no viable alternative) is a weakness. If this link is severed all control of the rover is lost and a system reboot is required. This is the architectural design around which this project will be based.

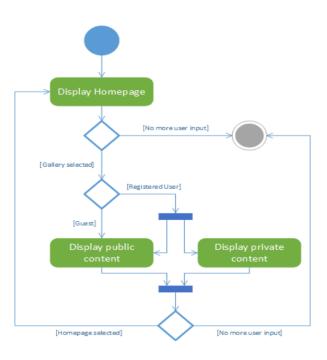

Figure 3. The initial activity diagram for the Rift Runner web site.

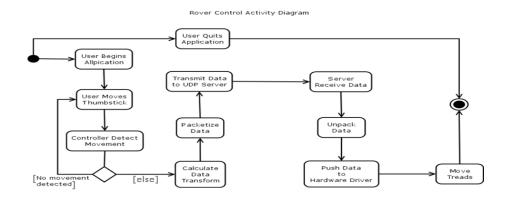

The Activity Diagram shown in see Figure 2 illustrates a high-level overview of user navigation options through the Rift Runner web site. Figure 4 on the other hand, illustrates rover control activities for the project. The user manipulates rover movements through a thumb stick and the UDP server is responsible for receiving, unpacking and pushing data to the hardware driver.

predetermined space. The rover control class converts these floats to integers that represent power and direction.

#### Figure 4. Rover Control Activity Diagram

Client-Server Architecure for the Rift Runner

#### Fig. 5. Client-Server Architecture

#### 2.2 Subsystem Descriptions

#### **Rover Controls**

The Rift Runner is controlled with the left thumb stick of an XBox 360 controller. The controller feeds floating-point decimals to the tank control class in the main application. The floats represent the x, y position of the controlling joystick within a finite, The rover control class then sends these conversions to the UDP Client that packages them and sends them to the UDP server on the Raspberry Pi. The Pi sends the data to the PWM that sends the data to the motor driver where they become power designations for the individual treads that will send the rover in any desired direction.

#### **Camera Controls: Controller**

While the main purpose of this project is first person piloting through the Oculus Rift, the Rift is not necessary for first person piloting. When piloting without the Rift the right thumb stick of an

XBox 360 controller controls the movement of the camera. The controller feeds floating-point decimals to the camera control class in the main application. The floats represent the x, y position of the controlling joystick within a finite, predetermined space. The camera control class converts these floats to integers between 160 and 630, and 460 and 150. These values represent the desired location of the camera within the allowable movement spectrum. The values are then passed to the servo controller on the rover and the camera is moved to the desired position. The controller also controls image and video capture. Image capture is mapped to the left trigger. When the left trigger is pressed,

whatever frame is currently on the camera is captured and pushed to the application, and from there the user has the option to save the image to the database or discard the image. For video capture the right trigger is depressed to signal the beginning of the capture and then depressed again to signal the end. The final feature of the controller camera control is a zero position button. In order to synch the Rift view and the camera position a zero position is needed. This zero position represents straight forward in regards to the rover heading and level with the horizon. This position is designated as 350, 350 within the servo space and when the A button is pressed the camera resets itself to this position and that is mapped to the current heading on the Rift.

#### **Camera Controls: Rift**

The Oculus Rift controls the camera on the rover with the motion of the user's head. The OR pushes floating-point decimals to the rift camera control class in the main application. These floats represent direction of the user's gaze based on an x, y location from the midpoint of the OR viewer. The rift camera control class converts the floats to integers between 160 and 630 on the x-axis and 460 and 150 on the y-axis. These numbers represent the minimum and maximum allowable positions of camera movement.

#### 3. Discussion and Lessons Learned

Over the course of the development cycle for the Rift Runner there were many factors that created limitations for the realization of the project goal. When everything is taken into consideration most of those can be placed under one of two headings: time or expertise. While each member of the group had individual expertise in areas that pertain indirectly to the project such as web development and programming, none of the team members had ever used those skills to produce anything like our final product. C++ was a new language to the team and we had to develop expertise in using the 3d printer, circuitry, and power management among others.

While the gathering of expertise made for a slow start, the hard deadline at the end of the semester made that slow start stressful. As we are all students, even mentioning time as a limiting factor seems like a "cop out". It is largely a limitation that we placed on ourselves, but in an environment devoted solely to development, our use of time cwould have been more focused. The Mythical Man-Monthdefines average output at 10 line of code per day. That definition implies a typical professional working environment, i.e. 8 hour workdays, of which 5 every week (at least)

are applied to the project. This schedule does not necessarily apply to all projects. In fact not once was there a day that did not involved the development of this project. The fact that we finished our project, with complete functionality, under these conditions makes us proud.

The main application and the Rift camera control class were developed by two different team members. They discussed what they were trying to achieve, made sure they were on the same page and built their code. One developer worked in Netbeans and the other used Microsoft Visual Studio, both applications were written in C++. When it came time to marry the code and test their compatibility we had little if any problems. It turns out that while Netbeans and Visual Studio are both IDE's that can be used to develop C++ applications they have slightly different library usage. That difference is enough to make applications native to one incompatible with the other. The Netbeans developer switched his IDE and the problem was quickly corrected.

Motors and motor drivers are necessary demons if one wishes to move some vehicle electronically. The motor driver that we chose to use has two inputs for power, a logic circuit and a power circuit. If the power circuit receives no charge then the motor will simply receive no power and will not move a tread. On the other hand, if the logic circuit receives no power the circuit board will overload and be destroyed. Fortunately we discovered this in research, not firsthand. It is imperative that we remember and heed this.

The last important piece of functionality that we developed was the video streaming. For early testing of the UDP connection a patchwork pipeline of tools was used to stream video. Once we tried to use this pipeline as our primary method we discovered that too much latency was present to make this a viable solution. Background research into video streaming revealed two likely candidates as fixes to our woes: OpenCV and GStreamer. The first attempt for a solution involved GStreamer, in retrospect it would have been advantageous to use OpenCV for the first attempt. GStreamer did not improve out latency issues. Once the OpenCV library became the primary solution focus latency improved and the project became closer to a success. The biggest hurdle during this process was cross platform compatibility, or lack thereof. The Raspberry PI OS is Linux based and the application was designed to run in a Windows environment, OpenCV was the only library we found that allowed us to easily implement this cross platform functionality.

#### 3.1 Lines of Code Comparison

Table II shows a summary of our predictions for the number of lines of code for the software side of our project. At the bottom of the table are estimates for the number of man-months required to complete the project as well as budgetary estimates. Our initial estimates were very naïve.

#### **3.1 Lines of Code Comparison**

| Section                               | LOC                           | LOC    | LOC   |  |

|---------------------------------------|-------------------------------|--------|-------|--|

|                                       | Initial                       | Design | Final |  |

| Main Application                      | 300                           | 300    | 565   |  |

| Vehicle – Controller                  | 50                            | 315    | 390   |  |

| Vehicle – Control Transmission        | 200                           | *165   | *360  |  |

| Camera – Rift Motion Tracking         | 10                            | 60     | 90    |  |

| Camera – Control Transmission         | 100                           | *165   | *360  |  |