# **SESSION**

# NOVEL SYSTEMS DESIGN AND APPLICATIONS + POWER EFFICIENCY AND MANAGEMENT

Chair(s)

TBA

# Livestock Management System

James Foulkes<sup>1</sup>, Peter Tucker<sup>2</sup>, Mariflor Caronan<sup>3</sup>, Rebecca Curtis<sup>4</sup>, Leslie G. Parker<sup>2</sup>, Chris Farnell<sup>2</sup>, Brett Sparkman<sup>2</sup>, Guoqing Zhou<sup>2</sup>, Scott C. Smith<sup>2</sup>, and Jingxian Wu<sup>2</sup>

Department of Electrical Engineering, Rose-Hulman Institute of Technology, Terre Haute, IN<sup>1</sup>

Department of Electrical Engineering, Rose-Human Institute of Technology, Terre Haute, IN Department of Electrical Engineering, University of Arkansas, Fayetteville, AR<sup>2</sup>

Department of Electrical Engineering, Northern Arizona University, Flagstaff, AZ<sup>3</sup>

Department of Electrical & Computer Engineering, Nissouri University of Science and Technology, Rolla, MO<sup>4</sup> <u>foulkejw@rose-hulman.edu</u>, <u>p.n.tucker@gmail.com</u>, <u>mdc259@nau.edu</u>, <u>rcr2f@mst.edu</u>, <u>lgparker@uark.edu</u>, <u>cfarnell@uark.edu</u>, <u>bsparkma@uark.edu</u>, <u>gzhou@uark.edu</u>, <u>smithsco@uark.edu</u>, <u>wuj@uark.edu</u>

Abstract—With the rising demand of the already large cattle industry, new techniques are being employed to aid in the tracking and monitoring of cattle herds. The wireless monitoring system described in this paper sets forth the framework for a large scale monitoring system to aid in the health and wellbeing of such herds. The system employs individual ear tags on each cow that monitored important vital signs such as core temperature, heart rate, and blood oxygen levels. Static access points were used in the network to continually track individual cattle movement as well as relay cattle health data back to the farmer's computer. This low power wireless system was successfully constructed and tested with overall favorable results. Sensor data was successfully sent back to the computer to be displayed in a graphical user interface along with the positioning information determined through triangulation for each cow. Future alterations to the ear tags would provide a more reliable product for marketable cattle monitoring systems.

#### Keywords- Bovine, Cattle, Ear Tag, Livestock Monitoring, Triangulation, Vital Signs, Wireless Sensor Network, XBee, ZigBee

#### I. INTRODUCTION

In 2010, the U.S. consumed approximately 26.4 billion pounds of beef, putting the retail equivalent value of the entire beef industry around 74 billion U.S. dollars [1]. For this level of consumption to be maintained, each cattle farmer must maintain an average herd size of around 100 or more heads of cattle [2]. Yet in 2010, due to factors such as bovine respiratory disease and other illnesses, the industry also suffered a significant loss of 1,234,500 cattle [3]. This results in considerable economic costs due to antibiotic treatment, losses due to death, and reduced herd performance.

#### II. RESEARCH OBJECTIVE

In order to offer farmers an efficient method of managing their livestock from the comfort of their homes, this project aims to employ a low power wireless sensor network to relay health and location data from the herd of cattle back to the farmer's computer. Where a farmer may have difficulty managing the herd 24 hours a day, the developed system would be able to track and monitor the well-being of each cow continually, and report all data back to a central PC. Proposed sensors would monitor pulse rate, temperature, respiration, and location information, in order to alert the farmers of any abnormalities, such as cattle leaving the specified grazing areas, early signs of illnesses, critical levels of body temperature or heart rate, and many others concerns related to the well-being of cattle.

#### III. FIVE-PHASE RESEARCH APPROACH

### A. Phase 1

In order to develop a working knowledge of the problem faced by farmers, research was done to lay out a basic method for monitoring bovine vital signs and location, and then relaying that information back to the farmers. As the first phase in this project's five phase process, which guides the research from hardware development through the implementation stage, information on bovine health was obtained through online articles, published papers, and personal conversations with local farmers and animal science professors. Using information gathered from these interviews and articles, specific vital signs were chosen to be monitored using sensors to detect the early signs of disease.

#### B. Phase 2

In the second phase of this project, the focus was on defining device specifications and initial device selection. This includes sensors, mounting equipment, microprocessors, wireless transceivers, and a base station, all configured for low power consumption. Several factors were considered throughout this process, such as power management, hardware compatibility, cost effectiveness, intrusion to the animal, and ease of overall use.

### C. Phase 3

The third phase of the project involved three simultaneous tasks to build a prototype of the system that transmits data from a cow through access points to a base station.

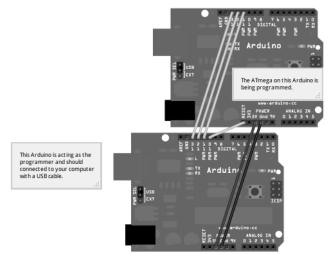

1) Development of mobile units and an ad hoc network

At the lowest level of the network, the wireless transceivers on the cow ear tags serve as the mobile units in the network. Together these mobile units form an ad hoc network through mesh networking, which automatically finds the shortest route to the nearest access point. The minimum distance routing scheme reduces the transmission distance of each datagram, which reduces noise and overall transmission errors in the system. Each mobile unit collects sensor information and an accompanying distance vector for the transceiver's routing table to be framed with a small dedicated microprocessor, and transmitted out through the transceiver.

#### 2) Development of access points and static network

The second task involved designing and building the access points to the basic service sets defined earlier as the ad hoc network. These access points collect the sensor information from the mobile units as defined through the ZigBee protocol and then route it through the extended service set to the base station. Again, each access point maintains a routing table defined using a distance vector routing scheme that allows the network to utilize the shortest route.

This process included a method for triangulation, which was done through the process of cell splitting. By setting the network up in this cellular fashion, the mobile units end up between at least three of the receivers at any given time. This allows for the towers to use signal strength measurements to triangulate the signal.

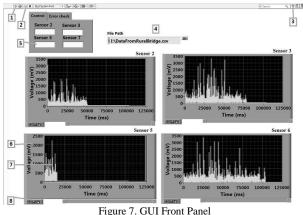

### 3) Implementation of a Graphical User Interface

The third task involved configuring a computer as a base station and building a graphical user interface (GUI). This receives the data from each mobile unit, displays it to the user in an easy to use format, and stores the data for use in a later phase of the project.

### D. Phase 4

Due to the large area and scale of some ranching operations the extended service set must be completely composed of wireless units requiring their own power sources. The fourth phase of the project involved research and implementation of power systems for both the mobile units and the access points. Research was also done on energy production and storage systems for regulation and distribution of power to th, transceivers and supporting components. An ideal power system does not require any replacement by the farmer for at least the lifetime of the cow, but the framework was set up for a failsafe mechanism to alert the farmer if the unit was close to failure or has experienced a power failure before the expected lifetime.

#### E. Phase 5

The final phase of the project was developing algorithms for data interpretation. This involved using the data from the mobile units to interpret when something is out of the norm, and alert the farmer. These alerts focus on issues such as cows escaping from the fence and early signs of disease. This makes the information easier to understand and use by making qualitative results from quantitative data.

#### IV. BACKGROUND

#### A. Measuring Cow Vitals

Previously, cattle health has been determined by visually assessing the cattle or a manual inspection by a veterinarian. Due to the amount of demand for beef and dairy cattle, it is essential for the farmer to have a quick and easy, as well as efficient, means of monitoring their cattle. In recent years, sensory devices have begun to be utilized to monitor cattle vitals such as temperature, heart rate, and respiration, since these have been determined to be the best indicators of early disease.

### 1) Temperature

One sensory device used to measure the cow's temperature is called a FeverTag, which is a tympanic thermometer device pinned to the ear with a probe inserted in the lower ear canal. This device flashes an indicator light when the temperature is greater than a set temperature such as  $103.6^{\circ}F$  [4]. Another sensory device used commercially is the CorTemp bolus, a large pill-like device, placed in a second stomach near the heart called the reticulum to measure core body temperature [5].

#### 2) Heart Rate

Not only has the CorTemp bolus been used to measure core body temperature, but it has also been used to measure heart rate. This bolus has been designed to identify the beginning of each pulse using a small waterproof microphone so that the times between consecutive pulses can be determined and then converted into a pulse rate [6]. Heart rate has also been previously monitored using a Polar heart belt, which acquires an animal's heart vector using a standard set of electrodes. This makes the Polar heart belt impractical for long term usage [5].

#### 3) Respiration

Not many sensors have been developed to directly measure the respiration of cattle, but one device that has been used to measure cattle respiration utilizes a thermistor attached to a nose stud in the animal's nostril. The temperature of the thermistor increases with respect to the ambient temperature as the animal exhales. The respiration rate can then be calculated by recording the number of times per minute the temperature rises and falls [7].

#### B. Tracking Unit Locations

The most common methods of guiding and tracking remote systems are based on the idea of triangulation. Triangulation is the process of determining the location of a point by measuring the time difference of arrival of a signal to three different receivers. Currently, the most common usage of a triangulation like technology is in GPS systems, which determine a position based on information from multiple satellites.

#### V. SYSTEM SELECTION

#### A. Cattle Temperature

Multiple temperature sensors were considered for measuring a cow's core body temperature through the ear, anus, or within a bolus. Due to the fact that the nearest location from the ear tag to get a reading for the core body temperature is the ear canal, a probe inserted at least two inches into the ear was the most convenient and least invasive method. The sensor chosen was similar to that used in the previously mentioned FeverTag. It was imperative that this probe be inserted into the lower ear canal deep enough for consistent readings without creating a nuisance to the cow. To prevent the probe from dislodging from the ear due to the cow's movement, the rigidity was strengthened by wrapping wire around the probe's length. In addition, the probe was selected due to it having an adjustable resolution for obtaining a more accurate temperature and a waterproof housing to prevent contamination from the elements.

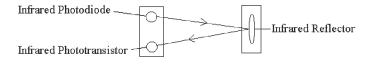

#### B. Reflective Pulse Oximeter

Low oxygen saturation of the hemoglobin or an abnormal heart rate may be early indicators of bovine illness. A common method of monitoring these vitals in humans is with a transmissive pulse oximeter. It is typically placed on the finger where it transmits light through the tissue, oscillating between an infrared light-emitting diode (LED) and a red LED, to a photo diode on the underside of the finger. Where the changing absorption of light from a single LED will indicate the pulsing of veins, two different wavelengths will be absorbed differently due to the oxygen in the blood, enabling the measurement of oxygen saturation by a light intensity comparison. The only feasible tissue on cattle to place a transmissive pulse oximeter would be the ear, however due to the hair on the backside that can alter data, a reflective pulse oximeter is necessary. The light from the LEDs is sent through the surface of the skin, where light reflects from the superficial vasculature back to the photo diode.

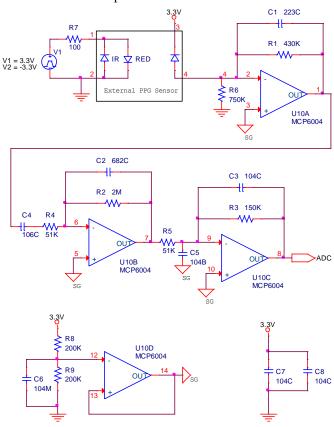

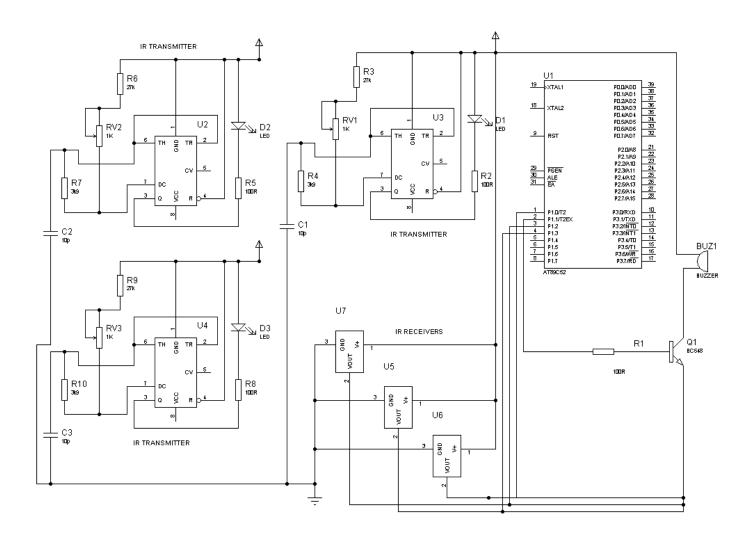

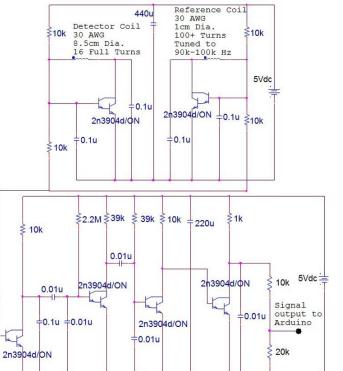

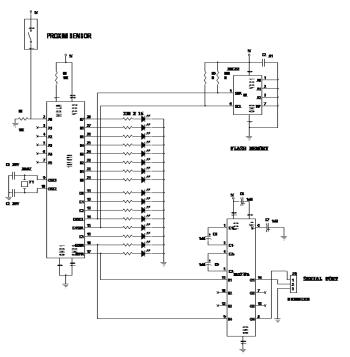

Figure 1 - Pulse Oximeter Schematic

The reflective pulse oximeter chosen featured a dual emitter and a photo detector embedded in a small chip, less than a centimeter squared in size and shown along with the sensing circuit in Figure 1. Since the device was intended for being used long term on a cow, the lower power and smaller size was more convenient for the ear tag.

### C. Environmental Humidity Sensor

Humidity negatively affects the signal strength, which increased data loss in the communication between wireless components. After reviewing different sensors that measure outdoor temperature and humidity, a digital relative humidity and temperature sensor was chosen. The humidity level acquired on the farm can be used to examine the signal strength dissipation. Also, the recorded temperature data serves as a baseline for the cattle temperatures throughout the day.

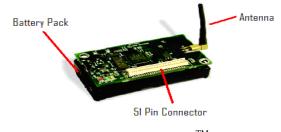

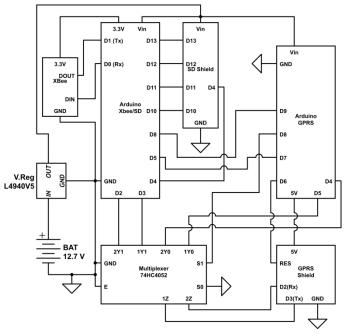

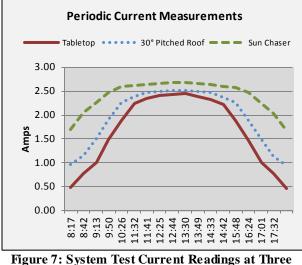

### D. Solar Panel and LiPo Rider

To run a remote sensory network the end points have to run off of a sustainable energy source since the nodes may not be easily accessible on a regular basis. This requires the nodes to incorporate a battery supply to sustain a level charge for the circuitry, while also having a method for recharging the batteries for extended operating durations to avoid unwanted disruptions. To recharge the batteries on the cows', solar panels were chosen over piezo-electric energy generation because solar power would give a predictable amount of power throughout the day for each cow, whereas any type of vibration or movement device would give off an unpredictable amount of power for each cow. Solar power was determined to be the only viable source of sustainable energy for the access points due to the impractical nature of other options such as wind power.

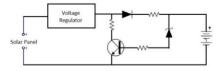

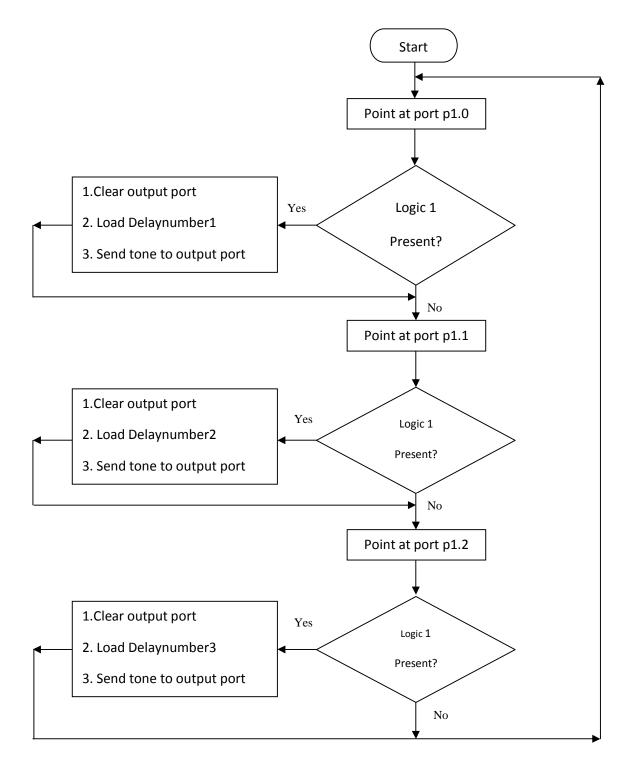

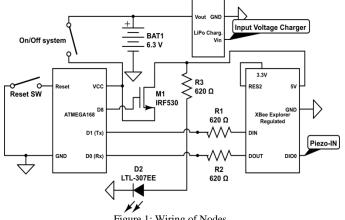

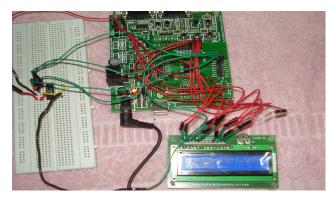

Figure 2 - Ear Tag Recharging Circuit

The solar panels on the ear tags were used to recharge small lithium ion button cell batteries through the circuit designed and shown above in Figure 2. The solar panels on the access points, however, were used to charge the batteries through a commercially available board called a LiPo Rider, which allows larger batteries to be charged. Each of these circuits allows the solar panels to run the transmitter directly in the event that the batteries are drained, and maintain a regulated voltage level.

#### E. XBee

In order to reduce the impact on the cows' normal activities, it was decided that all the sensorial information would be transmitted back to a central location through a wireless network. Due to the various sizes of farms, this wireless link could vary anywhere between a couple feet to a couple miles and be effected by all sorts of weather conditions. The XBee device, a wireless transceiver, was chosen because it works in all these scenarios with a maximum operating radius of two miles. XBees are also a good choice for this application because they are physically small, slightly larger than a quarter, and fit well within the space of an ear tag. The XBees also have a maximum transmitting power of 67mW, which makes them ideal for the low power endpoints of a remote sensor network. The conservation of power by these devices allows them to run in situations where they may not interact with people more than twice a year when the cows are being weighed and vaccinated. An added benefit of the XBee devices is that they follow the ZigBee protocol and have the

capability of setting up their own ad hoc networks, which made networking simpler.

Among the Xbee devices available, the programmable variant was chosen due to the sensor selection and special network requirements. The selected temperature sensors were one wire devices, which required the data collection to be done through the additional microprocessor on the programmable XBee devices. The ADC on this additional microprocessor was also used to sample the waveforms from the pulse oximeter's analog circuitry and place it into a digital frame.

### VI. DESIGN AND IMPLEMENTATION

#### A. Communication Links

As previously mentioned, XBee devices work off of a ZigBee networking scheme that divides the mobile units in the network into three main categories as determined by their function in the network. These three categories under the ZigBee protocol are the coordinator, router, and end device.

Due to the definition of these components in the ZigBee protocol, the networks all followed the star topology layout, and at the center of this layout is the network coordinator. The network coordinator sets up the network and allows other units to join the network assigning them network addresses unique to the coordinator's internal routing table.

The only links usually made with the coordinator directly are through routers, which like coordinators never sleep. Routers also act as the link between ad hoc networks of end devices and the coordinator, relaying the data from each device to the coordinator, and likewise from the coordinator to the end devices.

End devices, however, do in fact have the ability to sleep for periodic cycles and communicate during their uptime. These end devices, the third part of the networking scheme, are the outer most part of the star topology, and ideally communicate through the routers to the coordinator or to each other.

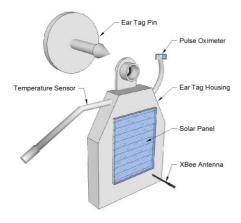

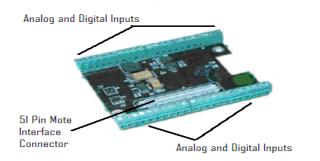

### B. Ear Tags

The main role of each ear tag, shown in Figure 3, was to collect information from the cow's vital sensors and relay those readings back to the coordinator at the farmer's computer. The data collected by the microprocessor on the programmable XBee was packaged together to send the combined packet back to the coordinator.

Whereas the main focus of the end devices is to collect data from the sensors and feed that information to the coordinator, the end devices also had to interact with the routers, or access points, so that the position of the cows could be triangulated. This was done through a frame acknowledgement to an AT request sent by an access point.

With large quantities of data being transmitted and received by the XBee devices, power management became an issue of great importance. To reduce the power consumption, the cows would be sampled only a few times an hour, during which time the XBees would be on. During the rest of the hour the XBee devices could be put in a sleep cycle so that the battery power would be conserved.

Figure 3 - Ear Tag Diagram

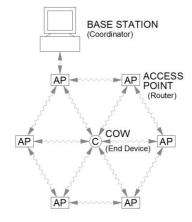

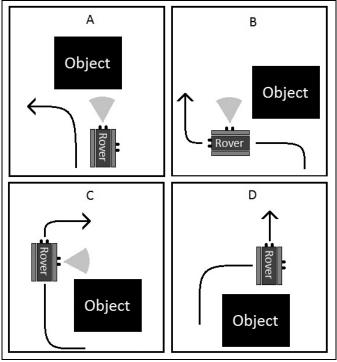

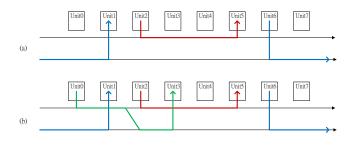

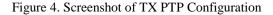

### C. Access Points

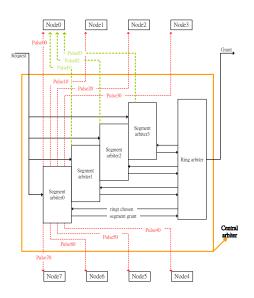

Generally, the purpose of a router is to serve as a switch or a range extender for a network so that the devices can communicate more effectively. Yet, in this network application, the access points, which acted as routers, were placed in fixed locations and used to triangulate the cows' positions through a maintained line of sight transmission. Each of these routers serves as an access point to the basic service set by routing the sensor information back to the coordinator through the shortest transmission path, so that a connection is always maintained between the cow and the coordinator. These access points were intended to be laid out in a hexagonal format, as in Figure 4, to maintain the possibility for at least three connections at all times and aid in the setup of large triangulation schemes. The setup of the network in this fashion also allows for the distance attenuation curve to be generated dynamically at the beginning of each triangulation routine. Instead, for the scope of this project the main access point was built with a temperature and humidity sensor to add a loss term to the propagation loss model when building the reference curve.

**Figure 4 - Network Layout**

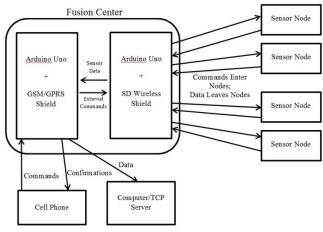

### D. Base Station

As the coordinator, the base station at the farmer's computer creates and hosts the network, which initially entails assigning every member of the network a 16-bit network address that could be used to create packet routes through the network. This position in the star topology doesn't have to be

filled by a programmable XBee, since the serial communication with the base computer could parse the frame and pull out the appropriate data packets. For the sake of speed, a programmable XBee was used to print out the values associated with each part of the data packet to the serial port along with a text header that could be parsed out as the values were read into the computer. As part of setting up the network, the coordinator sends the main access point the hardware addresses of the cows within the pasture, so that the main access point can then coordinate the AT-Command requests for the received signal strength from each of the routers to each of the cows.

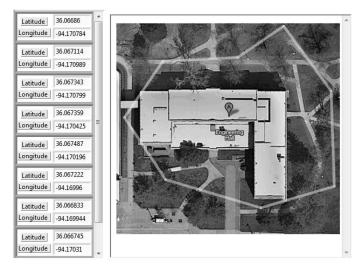

#### E. Tracking the Cattle

When installing this system on a farm, the GPS locations of each access point are taken. Due to the fact that GPS coordinates don't account for the curvature of the earth, standard triangulation techniques give skewed results when using GPS coordinates directly. For this reason the Universal Transverse Mercator coordinate system is used to give a system of projected planar coordinates in terms of eastings and northings, which can be easily used to calculate the correct triangulated position. This conversion is done by the computer when entering the GPS coordinates into the computer as illustrated in Figure 5 below.

Figure 5 - Fence Parameter Setup

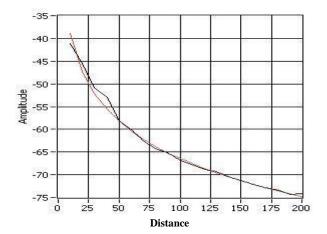

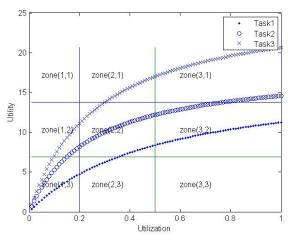

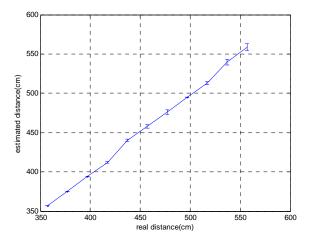

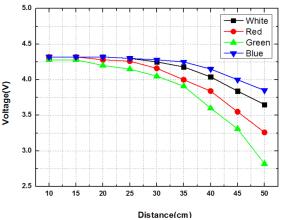

The equations used to compute the location of the cows in this project were derived by first making the assumption that around each of the access points was a sphere that had a radius determined by the strength of the signal it received. This distance is found empirically from a reference curve calculated during a calibration routine, as shown in Figure 6.

By solving the equations of each sphere for the point of intersection, the location of the common cow could be determined.

General form:

$$d^{2} = x^{2} + y^{2} + z^{2}$$

$$d^{2} = (x - x_{a})^{2} + (y - y_{a})^{2} + (z - z_{a})^{2}$$

Figure 6 - Propagation Attenuation Curve

Inclusion of three circles, as height is not a factor:

$$d_a^2 = (x - x_a)^2 + (y - y_a)^2$$

(1)

$$d_b^2 = (x - x_b)^2 + (y - y_b)^2$$

(2)

$$d_c^2 = (x - x_c)^2 + (y - y_c)^2$$

(3)

Subtract eq. 2 and 3 from 1:

$$d_a^2 - d_b^2 = (x - x_a)^2 - (x - x_b)^2 + (y - y_a)^2 - (y - y_b)^2$$

$$d_a^2 - d_c^2 = (x - x_a)^2 - (x - x_c)^2 + (y - y_a)^2 - (y - y_c)^2$$

Expand and collect terms:

$$d_{a}^{2} - d_{b}^{2} = (x^{2} - x^{2}) - 2xx_{a} + x_{a}^{2} + 2xx_{b} - x_{b}^{2} + (y^{2} - y^{2}) - 2yy_{a} + y_{a}^{2} + 2yy_{b} - y_{b}^{2}$$

$$d_{a}^{2} - d_{b}^{2} = (x_{a}^{2} - x_{b}^{2}) + (y_{a}^{2} - y_{b}^{2}) + 2(x(x_{b} - x_{a}) + y(y_{b} - y_{a})) \quad (4)$$

$$d_{a}^{2} - d_{c}^{2} = (x_{a}^{2} - x_{c}^{2}) + (y_{a}^{2} - y_{c}^{2}) + 2(x(x_{c} - x_{a}) + y(y_{c} - y_{a})) \quad (5)$$

$$V_{4} = \frac{(d_{a}^{2} - d_{b}^{2}) - (x_{a}^{2} - x_{b}^{2}) - (y_{a}^{2} - y_{b}^{2})}{2} = x(x_{b} - x_{a}) + y(y_{b} - y_{a})$$

$$V_{5} = \frac{(d_{a}^{2} - d_{c}^{2}) - (x_{a}^{2} - x_{c}^{2}) - (y_{a}^{2} - y_{c}^{2})}{2} = x(x_{c} - x_{a}) + y(y_{c} - y_{a})$$

$$V_{4} = \frac{(d_{a}^{2} - d_{b}^{2}) + (x_{b}^{2} - x_{a}^{2}) + (y_{b}^{2} - y_{a}^{2})}{2}$$

$$V_{4} = \frac{(d_{a}^{2} - d_{c}^{2}) + (x_{c}^{2} - x_{a}^{2}) + (y_{c}^{2} - y_{a}^{2})}{2}$$

$$V_{5} = \frac{(d_{a}^{2} - d_{c}^{2}) + (x_{c}^{2} - x_{a}^{2}) + (y_{c}^{2} - y_{a}^{2})}{2}$$

$$V_{5} = \frac{(d_{a}^{2} - d_{c}^{2}) + (x_{c}^{2} - x_{a}^{2}) + (y_{c}^{2} - y_{a}^{2})}{2}$$

$$V_{5} = x(x_{b} - x_{a}) + y(y_{b} - y_{a})$$

$$\frac{V_{4} - y(y_{b} - y_{a})}{(x_{b} - x_{a})} = x$$

$$V_{5} = x(x_{c} - x_{a}) + y(y_{c} - y_{a})$$

Substitute in for x:

$$V_{5} = \frac{V_{4}(x_{c} - x_{a})}{(x_{b} - x_{a})} + y \left( -\frac{(y_{b} - y_{a})(x_{c} - x_{a})}{(x_{b} - x_{a})} + (y_{c} - y_{a}) \right)$$

$$V_{5} - V_{4} \left( \frac{x_{c} - x_{a}}{x_{b} - x_{a}} \right) = y \left( \frac{(y_{c} - y_{a})(x_{b} - x_{a}) - (y_{b} - y_{a})(x_{c} - x_{a})}{(x_{b} - x_{a})} \right)$$

Solve for y:

$$y = \frac{V_5(x_b - x_a) - V_4(x_c - x_a)}{(y_c - y_a)(x_b - x_a) - (y_b - y_a)(x_c - x_a)}$$

Substitute solution for y into equation for x:

$$x = \frac{V_4 - y(y_b - y_a)}{(x_b - x_a)}$$

This position is then logged in the computer and saved so that the interactions of sick cattle can be tracked back to determine how the disease has spread and which cattle may be affected by the illness.

### F. Power Supply

When defining the battery supply required by each member in the network, several key factors had to be taken into account. Among these factors were relative network usage by each of the network members as well as the availability to renewable energy. For example, the access points were not constrained by size or weight, so they were free to have larger batteries and solar panels for recharging the batteries. The ear tags, however, were constrained by both size and weight requirements so that they would not cause ear drop in the cattle, which presents false signs of depression. Also, the solar panel chosen to recharge the batteries had to be powerful enough to supply the required current, but had to fit on the front of a standard ear tag to prevent excessive damage.

Access points handle the majority of the traffic in the network as they coordinate the AT requests required for triangulation as well as serve as the link between the end devices and the coordinator. For this reason, the batteries in the access points were chosen to meet the daily requirements for transmission in the event that the solar panels failed to recharge the battery at all. The value used to determine the relative transmissions for the day was calculated from the rated transmission power of the XBee devices and the total number of projected transmissions in a lossy environment with an equivalent projected error rate. As a result of having a larger battery to fill this demand, a larger solar panel was chosen to charge the battery through the LiPo rider board.

In addition to the ear tags being constrained by size and weight, they also sent and received fewer packets than the access points individually. As a direct result of this, the batteries could be smaller and therefore lighter weight. Yet, by having a smaller battery, the circuit has a smaller reserved power supply and relies more heavily on the ability for the batteries to be recharged periodically. A solar panel, being the most portable and reliable method of recharging the battery, is still limited by the need for sunlight to create current flow, which cannot be controlled on a cow that moves into shade to cool off. For this reason a balance was attempted to be made between the daily demand for transmissions by the ear tags and the amount of average solar energy projected to be harvested during the daylight hours.

### G. Software Integration

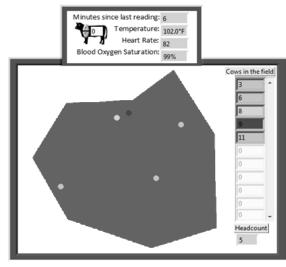

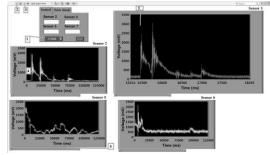

The Graphical User Interface (GUI) provides the farmer an easy to use method of viewing the statistics of the herd and logging the data along with additional information pertaining to symptoms and treatments regarding the cattle.

### 1) Live Data Display

As data is read into the GUI it is displayed on a front panel with each cow's position in the field as shown in Figure 7. A scrolling capability is provided to display each cow's most recent statistics in the table above the field, as also seen in Figure 7. This function can also be accessed by moving the cursor over the desired cow. By clicking on each cow, the individual statistics and history are displayed in a new window as shown in Figure 8.

In the front panel, when a cow's vital falls outside of the norm, the color of the corresponding dot changes from green to yellow, representing the cow's current status and warning the user of possible ailment. Similarly, a cow's status color will change to red and send an alert to the user when its condition is critical and needs to be manually inspected for illness.

Figure 7 - Herd Monitoring Window

In the case that more than one cow's vitals are falling outside the norm, the GUI enables the user to track the history of the cows' movements. This could help determine possible points of contamination such as a similar watering hole or food source.

#### 2) Data Logging

In order to provide a useful account of a cow's medical history, vitals are saved hourly for a seven day period. All proceeding vitals measured and recorded have a daily average going back for three months. Along with each individual cow's information, an average of the entire herd is recorded in a similar method. Saving the herd's average vitals allows the user to compare that of the individual to a norm of others in a similar environment, in addition to comparing cow temperatures with the corresponding outdoor temperature as illustrated in Figure 8.

Many situations may be presented where the farmer has a need to share the data he has logged in the program with others that don't have access to the cow's history. For instance, when the farmer interacts with a veternarian or a member of the Center for Disease Control, there is a method for printing out the health data associated with each cow as well as where the cows have been. This data is presented in an easy to read format that could also be given to buyers upon purchase of the cattle to ensure that the health information can be tracked in a responsible manner.

| 00                    | Last Reading<br>(24 hours max) | Temperature<br>(°F)                  | Heart Rate<br>(Beats per min)              | Blood Oxygen<br>Level (%) |

|-----------------------|--------------------------------|--------------------------------------|--------------------------------------------|---------------------------|

| 33                    | 9                              | 104.6                                | 80                                         | 99                        |

| Temperature (*F)      | - 10<br>1 3                    | Rate<br>3 3 3 3<br>Time (hours ago)  | <sup>56</sup> Oxygen<br>a 10 3 3 a<br>Time | in Blood                  |

|                       |                                | enrok 62.070 vilkovst skradovski kra | aas oo CX Mining                           | outăX ( <u>B</u> enz      |

| MM/DD/YEAR ^          | [Enter in Notes for corres     |                                      |                                            |                           |

| MM/DD/YEAR            | [Enter in Notes for corres     |                                      |                                            |                           |

| [Enter in notes here] |                                |                                      |                                            | A<br>T                    |

Figure 8 - Individual Cow Statistics

### VII. RESULTS AND DISCUSSION

Overall, the system worked as intended, although some alterations could be made for improvement. The tympanic temperature sensor gave accurate and consistent readings through all tests. However, when tested in the field on actual cows, the probes tended to fall out of the ear canal easily due to their unpredicted and excessive ear movements. Future models should incorporate thinner, longer, and stiffer probes to prevent dislodging due to ear movement. Probe length should change per individual cow due to differing ear sizes and tag placement.

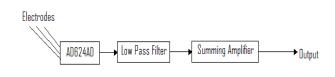

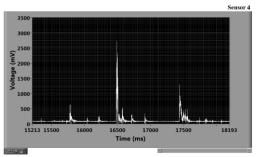

The pulse oximetry sensor on the ear tags went through several stages of development. A pulse oximeter was built with 5 millimeter LEDs and a similar sized photodiode, which was run through a basic current-to-voltage converter and single stage low pass filter to give a recognizable pulse waveform for both light frequencies to be sampled by the microprocessor; however, this circuitry would have had to have a multiple stage filter to add to the already large LED diode combination. For this reason a smaller LED diode integrated sensor was obtained from APMKorea to reduce the overall footprint of the device. This sensor supplied a signal to a four stage op-amp filter supplied along with the device, as shown in Figure 1. Despite much debugging and redesigning the circuitry accompanying the device in an attempt to better tune the filtered signal, the sensor failed to yield a consistently recognizable pulse waveform.

Field tests were initially done on creating an empirical propagation loss model to be utilized in triangulating the location of the ear tags. This test consisted of creating a curve from received signal strength at known distances from the receiver and then fitting this data with a logarithmic curve as shown in Figure 6. This allowed for future alteration of the curve due to other loss factors such as changes in relative humidity. When the data gathered from the received signal strengths were gathered from the access points, the fitted curve was interpolated to find the distance that corresponded to the respective signal strength. By this method the value for the relative distance between the ear tag and the access point was determined and then used in the triangulation equations in Section VI.E to determine the actual location of the ear tag. This process was done during testing at a higher resolution by using an average of data from combinations of three access points from a set of five unique access points. Based on this test the averaged result gave us the location of the ear tag within a range less than a foot.

### VIII. FUTURE DIRECTION AND CONCLUSION

To make this product more useful to farmers, other sensors could also be incorporated into the monitoring network to help track additional factors not considered in the scope of this project. For example, an XBee could be incorporated into the farmer's scale to track individual cattle growth through the early stages of its life. RFID chips could also be integrated into the system for additional benefits. In many areas, RFID tags are already utilized to track cattle through the transactions and transfers between farms. The incorporation of RFID tags in this network device would allow the health information of individual cows to follow them from farm to farm. This would allow all health information to be uploaded and tabulated in a large database that could aid in the tracking of bovine diseases throughout the cattle industry and improve the cattle vaccination process.

This wireless cattle monitoring project proved to be a viable proof of concept design that could aid in the tracking of health in cattle herds. Used by both farmers and researchers, a system based on this networking scheme could be utilized to more fully understand the health and natural patterns associated with cattle and many other species. This could one day be used as a vital link in a system of tracking and prevention of disease among livestock on a national level.

#### IX. REFERENCES

- [1] (2012, April 25). U.S. Beef and Cattle Industry: Background statistics and Information [Online]. Available: <u>http://www.ers.usda.gov/news/BSECoverage.htm</u>

- [2] (2009, Sept. 28). *Cattle: Background* [Online]. Available: http://www.ers.usda.gov/Briefing/Cattle/Background.htm

- [3] (2011, May 12). Cattle Death Loss [Online]. Available: <u>http://www.usda.mannlib.cornell.ude/MannUsda/viewDoc</u> <u>umentInfo.do?documentID=1625</u>

- [4] J. T. Richeson *et al.*, "Evaluation of an Ear-Mounted Tympanic Thermometer Device for Bovine Respiratory Disease Diagnosis," Arkansas Animal Science Department, Fayetteville, AR, 2011, pp. 40-42.

- [5] K. Smith *et al.*, "An Integrated Cattle Health Monitoring System," in *EMBS Annual International Conference*, NY, 2006, pp. 4659-4662.

- [6] A. Martinez *et al.*, "Ingestible Pill for Heart Rate and Core Temperature Measurement in Cattle," in *Engineering in Medicine and Biology Society Annual International Conference*, New York City, NY, 2006, pp. 3190-3193.

- [7] L. Nagl et al., "Wearable Sensor System for Wireless State-of-Health Determination in Cattle," in Engineering in Medicine and Biology Society 25th Annual International Conference, Cancun, MX, 2003, pp. 3012-3015.

# An Emergency Medical Service in IPv6 Network Environment

Tseng-Yi Chen<sup>1</sup>, Hsin-Wen Wei<sup>2</sup>, Ying-Jie Chen<sup>1</sup>, Wei-Kuan Shih<sup>1</sup>

<sup>1</sup>Department of Computer Science, National Tsing Hua University, Hsinchu, Taiwan <sup>2</sup> Department of Information Management, Tamkang University, Taipei, Taiwan

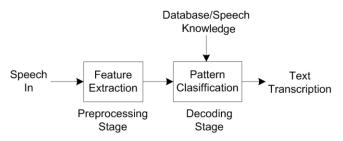

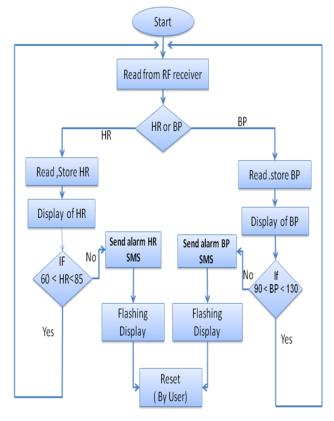

Abstract - Internet of Things (IoT) has been widely studied over the past decade. Recently, many research results of IoT, related to emergency system, smart building and medical system, are published. The key research issue of IoT applications is the ability to interact with physical world through computation, communication, and machine control. The emergency medical service is a very suitable application for IoT environment. Hence, we develop an emergency medical service based on IPv6 network environment. Emergency medical service is constructed by the biosensors, the healthcare information system and the notification component. The emergency medical service will process raw biological sensing data in bio-sensor module and show system's end-user the meaningful bio-information to notify them. In advance, medical service system also adapts the features of a speaker module. The role of the speaker module is regarded as a health alarm device. The emergency medical service can diagnose user's health according to the pulse information collected from biological sensor. Alert sound will be broadcasted by speaker module, if the emergency medical service detects abnormal situation from the sensing data. After alert sound is played, the speaker plays audio of each step according the standard first aid procedures, to tell peoples who are near to patients what to do. So, patients can obtain first aid operation from the near person to have their life saved. One additional problem need to be studied is the devices control. Most medical devices need to be connected to the internet. However, the number of IPv4 addresses is not enough. It is impossible to allocate IPv4 address to all wearable medical devices. Hence, we introduce IPv6 stack into the medical devices in order to realize the machine to machine (M2M) conception of the internet environment.

**Keywords:** IPv6, emergency system, wearable sensor, healthcare system.

## **1** Introduction

The research of the physical sensor device has garnered increasing attention owing to its technical importance in widespread applications, such as monitoring and surveillance in the military and biological detection [3,4]. Two critical issues for the development of sensor systems are the construct of innovative application and the solution of machine to

machine communication. In this paper, we develop an innovative emergency medical service system. Our medical service system contains three parts: hardware, software and cloud. This medical service system integrates biosensor and speaker module into the hardware platform. The medical diagnosis service is constructed in cloud platform and the medical service application is developed on Android system. Our medical service system provides online health diagnosing service and real-time condition feedback by the medical device. If user is in the emergency status, the medical system will notify the wearable device and the wearable device will help people who are near the patient to operate basic first aid guided by speaker module when the monitored person pass out.

Sensor applications originally entail components that interact with each other through complex network protocol. Hence, proper IP protocol can reduce the problem introduced by complex network protocol. Therefore, in this research, we also port IPv6 stack [1,2] to wearable medical device. With the help of the IPv6 stack, the medical device has the ability to communicate with handheld device or cloud service server via Internet environment.

In summary, this paper has two contributions in technical and research aspect.

*Technical:* In this research, we propose an innovative medical service application. The application can diagnose the monitored people's status according to sensing information from the biosensors. This system also gives a feedback to monitored people according to the result of diagnosis.

*Research:* We port IPv6 stack to medical service device. Based on IPv6 stack, we also develop a medical service system on these devices. Therefore, all Biosensors connect to medical service system through IPv6 Protocol. The healthcare application is developed on Android device and can control the medical device through Internet protocol. The communication between application and medical device is the machine to machine concept and is the important research issue for Internet of Things.

### 2 Related work

Traditionally, many researches put efforts on setting up a monitoring system inside the buildings. The research [6] reports their experience on the implementation, deployment, and operation of an indoor environmental monitoring network using WSN called SensorScope. To make the sensor nodes having long lifespan and working more efficient, some researchers [7] propose a clustering-based network specific for building monitoring. They also show that WSN is conducive to build environment monitoring system. Some applications that use WSNs for smart building are mainly for the energy saving purpose [8].

Nowadays, the deployment of a building control system is getting complicated due to different communication standards exist. In general, wireless sensor networks do not equip IP protocol in their system; therefore, different network routing algorithms are deployed. So, to connect their application system into IP-based internet requires the establishment of protocol translation stack at the boundary between internet and WSN. The translation stack transforms communication packet between non-IP packets of the WSN group and the IP packets in internet. The translation stack always stores a database of the local sensor node id and the outgoing TCP/IP port. The system need to inquire the database for delivering the message to destination machine when it receives a control message and sends a collection data to sink system.

There are also some solutions for solving the problem that variety of WSN standards are used for monitoring and saving energy in smart buildings. Some researchers [9] integrate WSNs with different service communication into a 'knowledge and information services' platform to support energy management feature, which can be accessed via a Web service to support inhabitant actions for reducing energy demand. In [10], the authors not only present a web servicesbased approach to integrate resource constrained sensor and actuator nodes into wireless sensor networks, but also implement an API to access services on sensor nodes. Their APT follows the architectural style of representational state transfer (REST). All research mentioned above do not take account of IP convenience for wireless sensor network applications.

Therefore, many research and standard groups [5, 15, 16] try to investigate and define the standard of IP stack in wireless sensor network. Sensor networks with IP support would eliminate the difference between WSN local area network (LAN) and Internet wide area network (WAN). Some research has been proposed in the IP-based WSN, e.g. mechanisms, security, and protocols. The concept of IP stack for smart object is proposed by IP for Smart Object (IPSO) Alliance [11] in 2008. After the IPSO concept is proposed, IP-based sensor network have been implemented [12, 13, 14] recently. These works include monitoring systems, healthcare applications and smart buildings. Those applications are based on IP transmission protocol. But they do not consider the issue that IP addresses is not enough. IPv6 protocol can solve this problem.

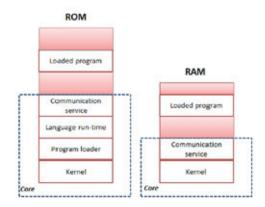

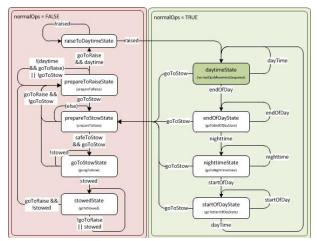

There are many WSN OS can be selected for porting, those are TinyOS, LiteOS, and Contiki. The most popular OS for WSN is TinyOS. TinyOS [17] is based on an event-driven programing model. TinyOS signals the event handler to deal the event when external trigger occurs. However, the programming language for TinyOS, that is NesC, is not commonly used by general programmer. For this reason, we choose Contiki OS as the operating system on our target platform.

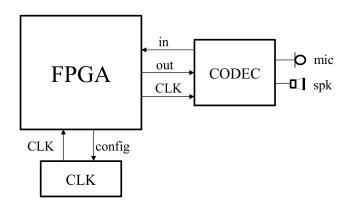

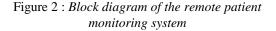

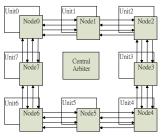

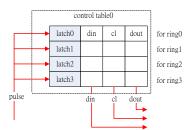

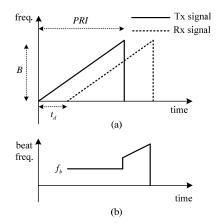

Contiki OS[18] is a small, open source and multitasking operating system. It is designed for embedded systems with small memory size. Contiki OS only consumes 2 kilobytes of RAM and 40 kilobytes of ROM. Contiki OS is also an eventdriven kernel and on top of which application programs is dynamically loaded and unloaded at runtime. Figure 5 shows the architecture of the Contiki OS.

Contiki's kernel is a light-weight kernel. Contiki OS can transmit the sensing data or forwarding message through communication service. The communication service is an important service in safe building application. We build up TCP/IP stack based on the service. After choosing the operating system, this research uses uIP stack as the communication stack in WSN application.

The uIP [19] is an open source TCP/IP stack for wireless sensor object. It is widely used in the embedded systems and several platforms. It also provide IPv6 stack for wireless sensor device. After survey of embedded TCP/IP stack, we choose uIP to build on the target system. It is a light weight TCP/IP protocol in WSN applications.

Hence, we propose an integrated IoT application solution based on concept of IP-based enable WSN that includes porting uIPv6 stack to sensor object, sensor information management system development, and speak module integration for application of escaping from disaster environment.

## 3 System design

The medical service system is composed of hardware platform and software stack. This section introduces the hardware and software component in emergency medical service system.

### 3.1 System architecture

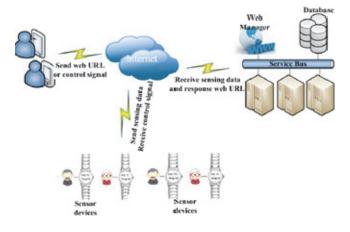

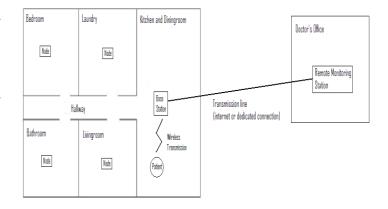

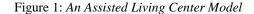

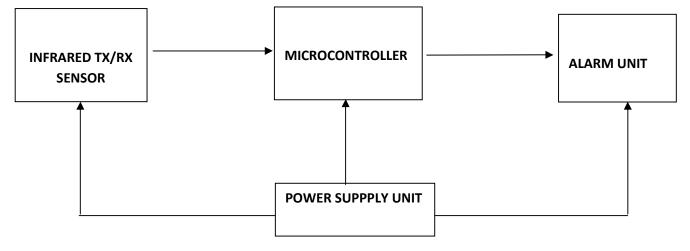

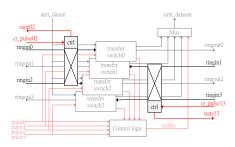

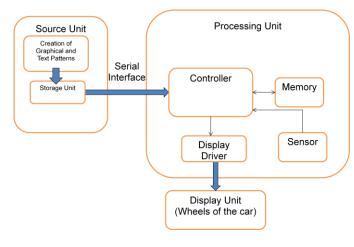

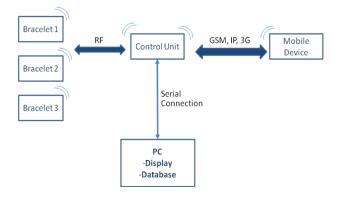

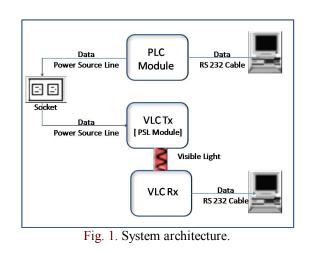

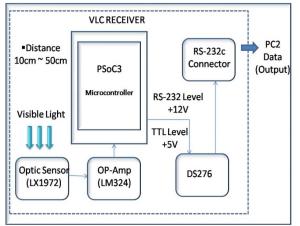

Fig. 2. Medical service system architecture

Figure 2 shows the system architecture of our emergency medical service system. We can see that our medical service system is composed of wearable health monitor device, medical service system in cloud platform and healthcare application on handheld device. The medical device system also integrates GPS module. The GPS module can locate the location of the monitored people. If the monitored people pass out, the medical service system will activate the GPS module on medical device immediately and the GPS module reports patient's location to medical service system. The medical service system will calculate a shortest path from hospital to patient's location and find the hospital that is nearest to the patient. Then, the medical service system sends the calculated path to the hospital to save the time for picking up the patient. The hospital system integration is in our future work

### 3.2 System Component Introduction

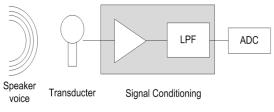

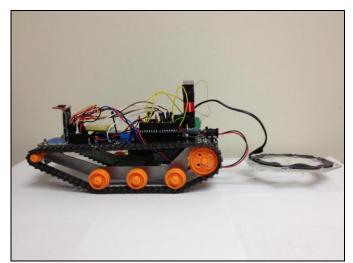

*Hardware platform*: The emergency medical service system is constructed by Piezo Buzzer sensor, temperature sensor, Speech Synthesizer Bee speaker module and ARM-based main board platform.

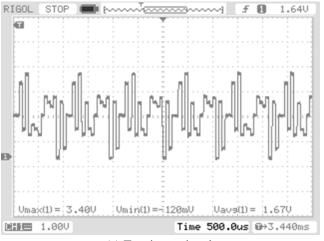

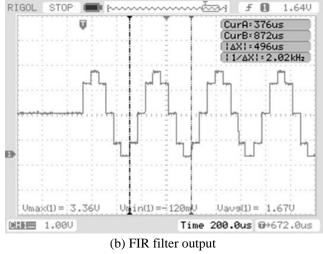

The Piezo Buzzer sensor is driven by square waves. It is cheaper than other pulse sensor. However, the Piezo Buzzer sensor will generate more noise in pulse detection. Hence, our medical system employs a suitable noise filtering algorithm to make pattern of pulse detection become normal. The speaker module used in our system is Speech Synthesizer Bee. It is pin-compatible with the Xbee and can be easily plugged into the sensor platform. This module is connected with Octopus II platform through UART interface.

*Software stack*: Our software stack is composed of system kernel, library layer and application level. We modify the system kernel in Linux in order to integrate some biosensors into embedded medical system. We also port IPv6 stack into embedded medical device. In application level, we develop a healthcare app on Android system. The healthcare apps can directly communicate with embedded medical device through IPv6 network.

## 4 The emergency medical service

The emergency medical service system must include wearable medical device integration, medical service deployment on cloud platform and application designed on mobile device, and the emergency medical service system based on IPv6 network.

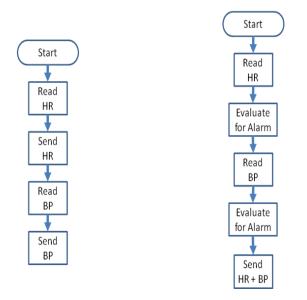

### 4.1 Wearable monitor device

The wearable monitor device is combined with three components: biosensors, speaker module and ARM-based main board. The biosensors are connected to ARM-based main board with UART and IIC protocol. The biosensors include Piezo Buzzer sensor, temperature sensor and pressure sensor. These biosensors can detect the biological information for human beings. The wearable monitor device will send the detected biological information to medical service implemented on cloud platform. The speaker module is integrated with ARM-based main board through UART interface. The speaker module can play alert sound to help the monitored people to realize their health condition.

### 4.2 Medical service on cloud

We deploy the noise filtering algorithm and medical diagnosis system on cloud platform. The noise filtering algorithm helps our medical service system adjusting and correcting the biological information detected by biosensors. The noise filtering algorithm can help our medical diagnosis system to get more precision diagnosis. If the user is in bad health condition, the medical service sends alert to wearable device and the device notify the user the current situation by speaker. If the monitored people pass out, the medical service will send the first aid procedure step by step to wearable monitor device and also delivers the path information between the patient's location and the nearest hospital

### 4.3 Application designs

The application is developed on Android system. The functions of our application include real-time pulse data

monitor, health condition in history view and the wearable monitor device system configuration. The application communicates with the wearable monitor device and medical service platform through IPv6 stack

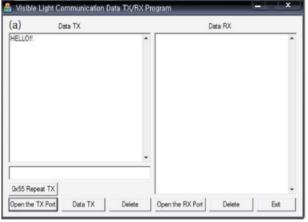

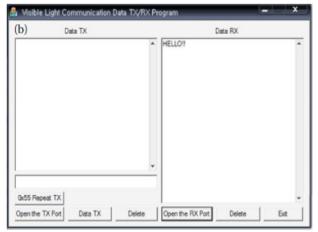

## **5** System demonstration

First, we describe the application scenario of our medical service system. Then, our demonstration will show the wearable monitor device with execution result, the medical service system, and the healthcare application.

### 5.1 Application scenario

Here are two demo cases in our demo scenario

# 5.1.1 The wearable monitor device could save patient's life.

The user needs to wear the medical device, such that the wearable medical device can save his life when he passes out and notify other people around the patient by speaker module in wearable device. Note that, the medical device is integrated with a speaker module and can plays first aid operation step by step when the user is in the emergency status.

# 5.1.2 The medical service system can conserve time to hospital.

Our wearable device equips a GPS module. Therefore, the medical system can send the location of the patient to the ambulance as soon as possible

### 5.2 System evaluation

#### 5.2.1 Health monitor platform

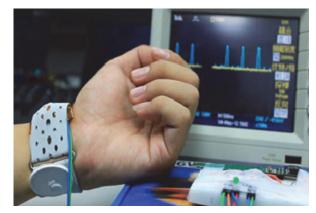

Figure 3 shows the health monitor platform .The wearable monitor device could detect the status of people's pulse, temperature and pressure. We also integrate a speaker module into the wearable device. And the wearable device will sends the biological information of the user to the medical service platform and the healthcare application.

Fig. 3. The wearable monitor device

### 5.2.2 Medical service on cloud

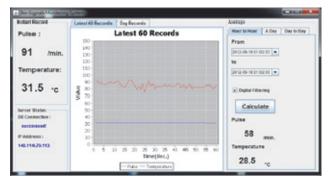

We deploy our medical service on cloud platform. The medical service includes noise filtering in biological data sensing, ECG information presentation and medical diagnosis. Our medical service also could give user feedback about their health condition. Figure 4 shows our medical service system. The server display last ten records of pulse detection and shows the real-time biological information of the GUI lefthand side. User can query specific history information of the GUI righthand side

Fig. 4. The medical service on cloud platform

### 5.2.3 Healthcare application

Fig. 5. Healthcare application demonstration

We also develop a mobile application on Android system. Users can monitor real-timeEGC information in

application and change the view of the history data list. The application also provides the configuration of the wearable device system. All of the information communication in the application is on the IPv6 network. Figure 4 shows our healthcare application on Android system.

# 6 Conclusion

Handheld devices become indispensable equipment in the daily life of the people. Hence, we propose a complete medical service system. The medical service system includes wearable monitor device, medical service system on cloud and healthcare application. And the medical service system is also built in IPv6 network environment. The medical service integrate speaker module to provide feedback information from medical service system. This is an innovative application in biological information system.

# 7 Acknowledgement

We would like to thank the National Science Council of the Republic of China (Taiwan) for financial support of this research under contract numbers NSC 101-2221-E-007-128-MY2, NSC 101-2219-E-007-007 and NSC 101-2221-E-032-067.

# 8 Reference

[1] S. Deering and R. Hinden, "Internet Protocol, version 6 (IPv6) specification," RFC 2460, 1998

[2] Adam Dunkels, "Full TCP/IP for 8-bit architectures," in Proceedings of the 1st international conference on Mobile systems, applications and services, MobiSys'03, pages 85-98, 2003

[3] I Lee, O Sokolsky. "Medical Cyber Physical Systems", 47th ACM/IEEE Design Automation Conference (DAC), pp. 743-748, 2010

[4] S Kannan, "Wheats: A Wearable Personal Healthcare and Emergency Alert and Tracking System", European Jounal of Scinetific Research, Vol 85 No. 3, pp 382-393, Sep. 2012.

[5] G. Montenegro and N. Kushalnagar, "Transmission of IPv6 Packets over IEEE 802.15.4 Networks", draft-ietf-6lowpan-format-01, Internet-Draft, work in progress, October 2005

[6] Schmid Thomas, Dubois-Ferrière Henri and Vetterli Martin, "SensorScope: Experiences with a Wireless Building Monitoring Sensor Network," Workshop on Real-World Wireless Sensor Networks (REALWSN'05), Stockholm, June 2005 [7] Qifen Dong, Li Yu, Huanjia Lu, Zhen Hong, Yourong Chen, "Design of Building Monitoring Systems Based on Wireless Sensor Networks," Wireless Sensor Network, Vol.2 No.9, PP.703-709, September 2010

[8] Yuvraj Agarwal, Bharathan Balaji, Rajesh Gupta, Jacob Lyles, Michael Wei and Thomas Weng, "Occupancy-Driven Energy Management for Smart Building Automation," Proceedings of the 2nd ACM Workshop on Embedded Sensing Systems for Energy- Efficiency in Building, pp. 1-6, 2010

[9] Hanne Grindvoll, Ovidiu Vermesan, Tracey Crosbie, Roy Bahr, Nashwan Dawood and Gian Marco Revel, "A wireless sensor network for intelligent building energy management based on multi communication standards – a case study", ITcon Vol. 17, pg. 43-62, 2012

[10] Lars Schor, Philipp Sommer and Roger Wattenhofer, "Towards a Zero-Configuration Wireless Sensor Network Architecture for Smart Buildings," Proceedings of the First ACM Workshop on Embedded Sensing Systems for Energy-Efficiency in Buildings, pp. 31-36, 2009.

[11] A. Dunkels and J. Vasseur. "IP for smart objects alliance.", Internet Protocol for Smart Objects (IPSO) Alliance White paper No.2, September 2008.

[12] M. Durvy, J. Abeill'e, P. Wetterwald, C. O'Flynn, B. Leverett, E. Gnoske, M. Vidales, G. Mulligan, N. Tsiftes, N. Finne, and A Dunkels. "Making Sensor Networks IPv6 Ready." In Proceedings of the 6th ACM conference on Embedded network sensor systems, pp. 421-422, 2008.

[13] J. Hui and D. Culler. "IP is Dead, Long Live IP for Wireless Sensor Networks." In Proceedings of the 6th international Conference on Embedded Networked Sensor Systems, Raleigh, North Carolina, USA, November 2008.

[14] B. Priyantha, A. Kansal, M. Goraczko, and F. Zhao. "Tiny web services: design and implementation of interoperable and evolvable sensor networks." In Proceedings of the 6th ACM conference on Embedded network sensor systems, pp. 253-266, 2008

[15] IETF working group 6lowpan, "IPv6 over Low power WPAN (6lowpan)", Available: http://www.ietf.org/html.charters/6lowp ancharter.html

[16] Adam Dunkels, "The Contiki Operating System 2.x", Available :http://www.sics.se/~bg/telos/html/

[17] Philip Levis, Sam Madden, Joseph Polastre, Robert Szewczyk, Kamin Whitehouse, Alec Woo, David Gay, Jason Hill, Matt Welsh, Eric Brewer, and David Culler. "TinyOS: An operating system for wireless sensor networks". In W.

Weber, J. Rabaey, and E. Aarts, editors, Ambient Intelligence. Springer-Verlag, New York, NY, 2004.

[18] Dunkels A., Björn Grönvall and Thiemo Voigt. "Contiki

a lightweight and flexible operating system for tiny networked sensors." In LCN '04, pages 455–462, Washington, DC, USA, 2004. IEEE Computer Society.

[19] Adam Dunkels, "uIP - A Free Small TCP/IP Stack," 2002. http://www.chuandong.com/cdbbs/upload/2007-10/11/20071011951453508.pdf

# Design of a FPGA-based Virtual Bus Interface System for Reducing IOs in Hardware-in-the-Loop (HIL) Real-time Simulation

## K. Strell, D. Mackellar, and Y. Jung

Electrical and Computer Engineering, Gannon University, Erie, PA, USA

Abstract - The complex embedded systems of locomotives require a vast amount of the Hardware-in-the-Loop (HIL) testing before manufacturing. Various simulation efforts are required to commit testing of the target embedded systems. Therefore, development of the most effective systems is necessary for efficient and accurate verification of the embedded systems. Since most of the verification is complete on the software, simulator seldom uses behaviors of IO operations, which are critical in real-time applications including embedded systems for locomotives. This paper proposes a bus interface system to replacing the existing massive IO cards in an embedded system integrated in a locomotive simulator for providing reconfigurable extension while maintaining required IO specifications including IO access speed and signal fidelity. The developed bus interface system is integrated to a modified Modbus (FEBus) and the main simulator computer. The bus interface system is implemented with FPGA including the NIOS II processor core with associated other IP cores. In order to evaluate capability of the HIL simulation with the developed system, a couple of interface protocols, such as PCI over a PMC connection and Gigabit Ethernet UDP/IP, are thoroughly tested.

**Keywords:** bus interface system, hardware-in-the-loop simulation, real-time simulation

# **1** Introduction

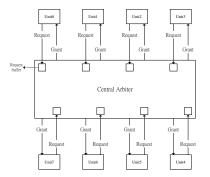

A control system of a contemporary locomotive comprises of heterogeneous embedded systems that communicate with each other to accomplish the desired complexity and accuracy for concurrently driving numerous actuators on the locomotive. The employed actuators are ranged from power electronic circuits to display screens. The actuators are required for sharing data between the embedded systems integrated on the locomotive to operate the desired functions.

The interface between the embedded systems is a means for efficient control and user interaction. However, it also increases the complexity of the system verification. In particular, error propagation at the system level verification is significant because an error at the system level could be often influenced by multiple components in its subsystems. Thus, inter and intra function verifications via the interface are necessary for verification of the embedded systems [1]. Given the complexity of the embedded systems, HIL simulators are the most efficient means of validating the hardware and software of these systems. However application specific simulators such as [2] and [3] would require an infeasible number of simulators to cover all of the embedded systems and would make it extremely difficult to simulate the systems together. Therefore in the locomotive simulators used currently the embedded systems in question become the UUTs and the other pieces of the locomotive are simulated in software with electrical signals interfacing the physical components to the modeled components [4].

In order to bear such increasing complexity at the system level verification, the simulators are required to cover the entire embedded systems under the same or compatible environment. In particular, our target system, a locomotive, comprises various heterogeneous embedded systems that are integrated through several partitioned interface hardware systems. Furthermore, the number of components employed in each subsystem proportionally raises the complexity and cost of the simulations.

Building a simulator is a daunting task in terms of its development time and cost. Therefore, including application specific features into a simulator is not preferable. Consequently, one of the best solutions to this issue is to maintain the simulator's capability with little or no changeability. This was evident in the first attempt at reducing IO, the Slim Sim in which the main modified Modbus (FEBus) device, the Consolidated Input Output (CIO) unit was removed completely. This yielded a simulator with reduced IO but also reduced functionality.

After the full limitations of the Slim Sim were understood there stood two distinct paths that could be taken to obtain the desired IO reduction while also maintaining the testing integrity. Both of the options involved removing at least part of the FEBus devices in the simulators. The first option was to virtualize the entire FEBus device so the control software would be run on a modeled device [5]. The second option would be to use a bus interface card [6] to mimic the IO cards on the FEBus of the CIO leaving the processing card intact to run the control software.

Section 2 describes the architecture and operation of the bus interface system. Section 3 expresses evaluation of the bus interface system with the simulation results and analysis of the simulation results. The conclusions and future work are depicted in Section 4.

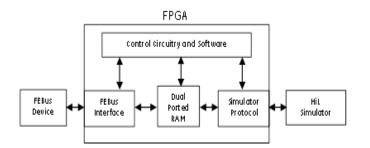

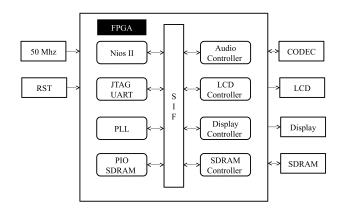

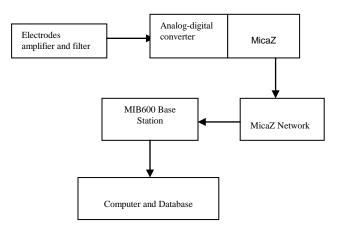

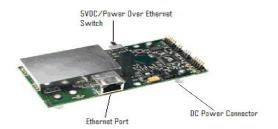

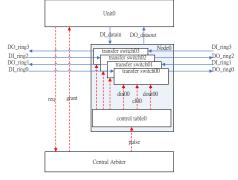

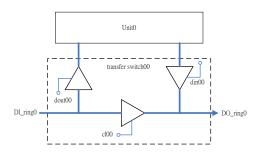

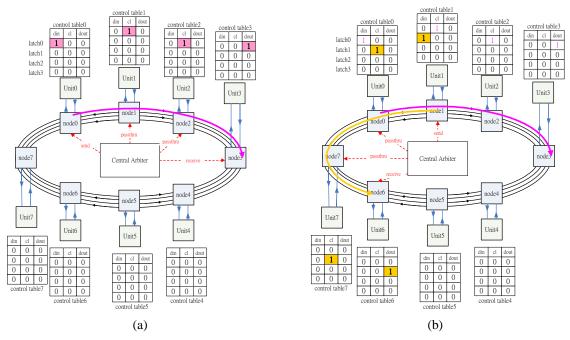

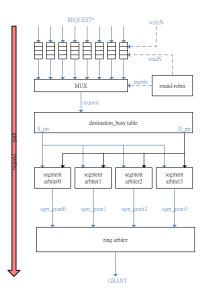

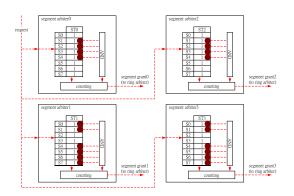

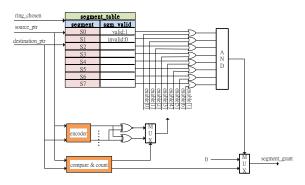

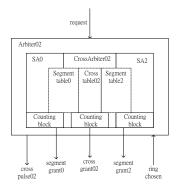

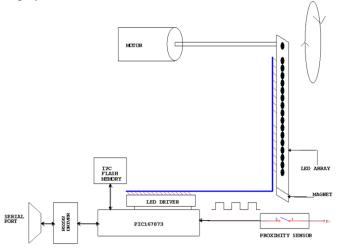

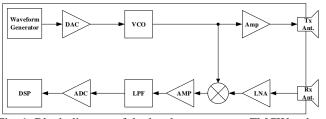

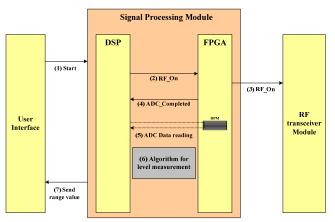

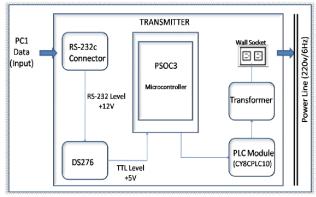

Figure 1. A Block Diagram of the FPGA-based Virtual Bus Interface System

# 2 Architecture of the Virtual Bus Interface System

As addressed in the previous section, the "Slim Sim" was created by eliminating the CIO unit. The SlimSim forces the control system on the locomotive to run in a reduced mode, which recognizes the CIO unit in a disabled state. The reduced mode in the simulator prevents some components from simulating at the component level. The simulator, however, retains its systems level simulation capability. More specifically, the simulator yields the ability to perform a full HIL simulation with a reduced cost if the IO portion of the CIO unit is removed but the processing card is remained.

The FEBus interface card, shown in Figure 1 as a block diagram, is composed of four major components: the FEBus interface, dual-ported RAM, simulator protocol, and the control circuitry and software. The FEBus interface is responsible for responding to the FEBus master, reading and writing the RAM when it is instructed. The simulator protocol, either the PCI interface or UDP Ethernet, is the data manager for the simulator side. It moves data according to IO point, writing outputs from the simulator into the RAM and reading inputs to the simulator from the FEBus data in RAM. The RAM is used to hold all the data for the IO points that would be controlled using the IO cards in a full HIL setup. The control circuitry and software consists of the NIOS II processor running software to manage the DMA moving data to and from the simulator protocol. In addition, it runs the software required to operate the simulator protocol, either a TCP/IP stack for UDP or a PCI driver for the reflective memory card.

### 2.1 FEBus for Virtual Bus Interface

After executing a simulator without CIO, it was evident this approach is a feasible solution or maybe one of the best ways for simplification. Although the simulator could be alleviate the signal congestion during the simulation, involving CIO throughout the simulation prohibits the simulator from its intended simulation capability. We realized that a means to include the processing component of the CIO unit could be a viable solution while removing the interface cards from the simulator. In the current practice, a simulator directly accesses the FEBus for reading and writing data to and from during simulation. Thus, the simulator can obtain the available CIO data without involving having any interface card.

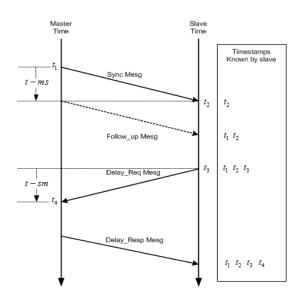

## 2.2 Bus Interface Protocols for HIL Real-time Simulation

In order to transmit and receive data to and from the simulator, a preferred interface needs to be selected. This interface is also intuitively interconnect the existing simulators while satisfying important constrains including the simulator time of the IO operation via the interface. In particular, a key the interface constraint identified is timing difference between the target simulator and the interface hardware. For instance, the interface hardware provides a 10ms sampling rate. An access time of the simulator is relatively slower than the signaling time over the interface hardware. In order to overcome this issue, we adopted a reflective memory network and a dedicated Ethernet between the interface hardware and the simulator. We evaluated a couple of the interface protocols for our implementation.

The reflective memory network approach [7] can facilitate integration of the interface hardware with the simulator. A reflective memory network card seamlessly integrates and updates to the existing ring or hub by propagating the changes to its memory across to the other nodes on the network. Since data integrity is one of the key aspects for interface, data from the FEBus must be written to its dedicated ranges of the addresses. In other words, the data written via the FEBus must be not overwritten by any other simulators. However, this approach requires implementing the PCI or PCIe bus architecture (i.e., GEIP or General Standards Corp). For instance, the GEIP PCI Reflective Memory card [8] employs the PCI bus.

The PCI bus architecture requires operating in the host bridge mode, which always permits a controlling master to access the bus. In order to expedite our design process, an FPGA-based host-bridge capability is chosen. The PCI Reflective Memory card is connected to the PCI bus architecture implemented on the FPGA via a PMC connection [9]. In addition, a driver needs to be developed. As the PCI memory card is configured through assembly level programming, the driver is configured as a memory mapped variety. In this approach, one of the most critical portions in the design is to manage the PCI configuration unlikely an operating system (OS) usually take care of this kind of operation.

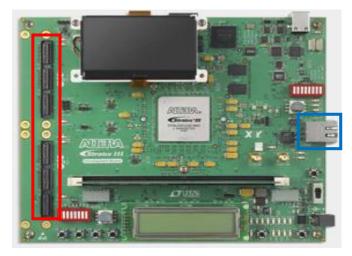

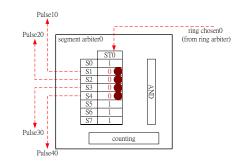

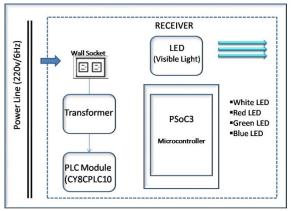

Another communication protocol selected is the UDP over a Gigabit Ethernet connection. This protocol is inexpensive to integrate into the simulator. In addition the protocol provides an intuitive means to utilize an interface board for monitoring data over the FEBus without any special hardware. The protocol was implemented to the same FPGA used for the PCI. The Altera's triple-speed Ethernet core and the RJ-45 connector on the Stratix III Development Board [10] were used for our implementation. Figure 2 shows the location of the RJ-45 on the development board in the blue box. The triple-speed Ethernet core [11] employs a software driver allowing the NIOS II microprocessor to open and maintain a UDP connection in a client-server relationship with the simulator.

Figure 2. The Virtual Bus Interface System Implementation with Interface Connections on the Altera Stratix III Development Board

While the preferred interface protocol was the PCI Reflective Memory card, the design was almost unable to prototyped. The Stratix III FPGA board, however, provides dedicated pins for a PCI bus interface with 3.0V signaling. Unfortunately, the same pins are assigned for other IOs. Without ability to access the PCI pins directly, the UDP connection was chosen for the simulator interfacing protocol.

# 2.3 Implementation of the Virtual Bus Interface System

The virtual bus interface system developed is comprised of four components—(1) the FEBus interface, (2) the UDP simulator interface, (3) the dual-port SRAM, and (4) the NIOS II microprocessor core. The FEBus interface responds an address for each IO card in the CIO unit. Thus, the FEBus interface eliminates any additional hardware on the simulator sides. The UDP simulator interface transmits data to and receives data from the simulator by delivering the value of the IO points to and from the simulators. Dual-port SRAM permits to read and write operations simultaneously if necessary. In particular, the data at the same address need to be accessed at the same time. The NIOS II microprocessor initializes the bus interface system and controls data flow.

The primary interface logic including the FEBus and the UDP simulator interfaces, the SRAM, and the microprocessor was implemented on an Altera Stratix III FPGA development board. The FEBus connections utilize one of the two High-Speed Mezzanine Card (HSMC) interfaces. The HSMC connections are located on the left side of the development board in the red box in Figure 2. These connections were converted to standard 1" headers using a third party breakout board. The one inch headers allowed the use of standard

ribbon cable which could be soldered to ribbon cable on the FEBus connector of the CIO unit.

The UDP simulator interface utilizes the Altera's triple speed Ethernet core including the MAC logic and PHY circuitry. The UDP simulator interface also exploits a software driver, which the two scatter-gather DMA cores read and write the associated Ethernet buffers. The UDP connection between the simulator and the IO board was designed for delivering a packet in every 250us.

On the other side of circuitry, the FEBus interface transmits data to and receives data from the dual-port SRAM via the address translation logic under the control of the bus master. The bus master is an IO manager for other embedded systems on the locomotive. The hardware of the FEBus was tailored to each IO slot. The developed FEBus interface responds to addresses on the bus as monitored by the bus master. The FEBus interface accesses the dual-port SRAM via the Altera's memory mapped Avalon connection.

The remaining hardware was built with Altera's COTs cores available in the Qsys tool. The Qsys tool allows the building of digital circuits in a graphical fashion and is part of the Quartus design software. Using this tool, frees the designer from having to make individual signal connections as they are grouped together logically and connected using a relatively simple graphical interface. The FEBus logic was brought into the Qsys tool for use in the design using a built in wizard for importing user defined circuitry.

| Quartus II 32-bit - C:/altera/sgdma2_test/strat   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | atixill_3si150_dev_niosii                           | standard                                                                       |                   | 🍂 Start            |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------|-------------------|--------------------|